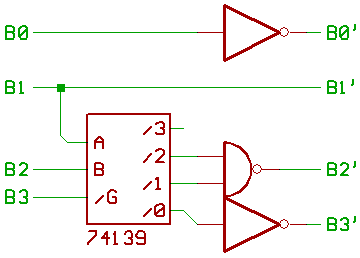

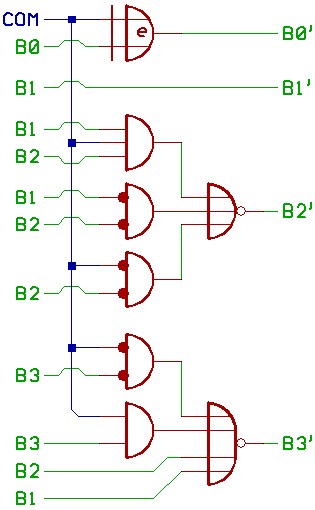

Now a small collection of schematics from

Fairchild Fast Applications Handbook,

1987, Page 5-45:

Warning:

For an input range of 0..9, all of the 9s complementer

schematics are supposed to return 9..0.

But when sending 10..15 into those 9s complementers,

the output is undefined.

Clear text: In that case, don't expect two schematics

to give you identical results...

or correct results, that is.

COM=0: B' = B.

COM=1: B' = 9s complement of B.

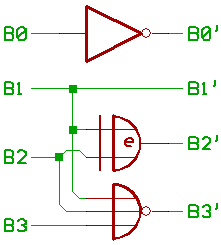

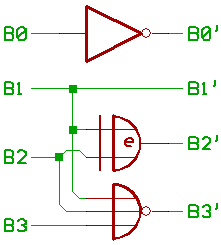

The 9s complementer which is used inside the

74582 adder/subtractor.

Ok, my notation is a bit different from the original.

Warning: for COM=0:

B' is supossed to be B... for input values from 0..9.

Input values of 10..15 at B may be turned into garbage at B'.

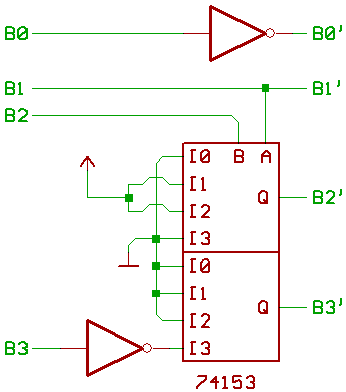

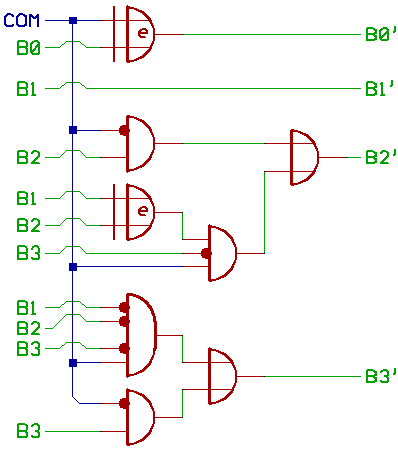

Just toying with the equations, ignore this picture.

Don't know, if this here really works...

[HOME] [UP]/ [BACK] [1] [2] [3] [4] [5] [6] [7] [8] [NEXT]

(c) Dieter Mueller 2012