First, we are starting with a concept

which you are already supposed to know...

from some "ALU design" articles, for instance.

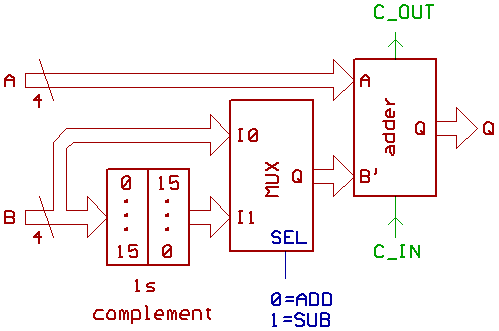

A simple 4 Bit binary adder/subtractor:

Q=A+B:

C_IN is a high_active carry,

the multiplexer routes B to the adder B' input,

it's simple.

Q=A-B

is less simple to understand.

Because we are using an adder,

we need to do something like Q=A+(-B).

In other words: we have to complement B

into a negative number.

-B is the 2s complement of B.

As we know from the school books:

in order to convert B into a negative number,

we first have to invert B into /B, then to add 1.

/B is the 1s complement of B.

The box labeled "1s complement" only contains

four 7404 type inverters.

For instance:

the 1s complement of binary 0000 (decimal 0)

is binary 1111 (decimal 15).

"But how to increment /B ?", you may ask.

The simplest way is to set the ALU carry input to 1.

So Q=A-B is done by this hardware as Q=A+/B +1

And because of that, C_IN now is a low_active borrow

instead of a high_active carry.

"Yeah, every little kid knows this,

but why is that guy lamenting

about the boring basics again ?"

Answer:

To give you a better chance of understanding this:

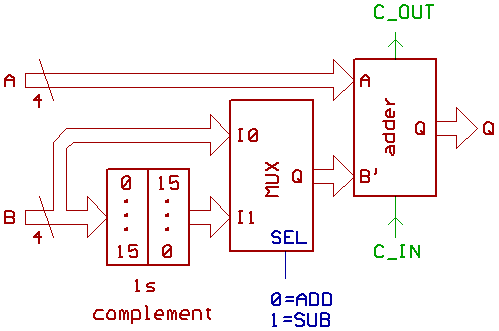

A 4 bit BCD adder/subtractor.

The concept is very similar to the binary adder/subtractor,

only that we are using a 10s complement of B this time.

To be more exact: for Q=A-B, we do a 9s complement of B,

and C_IN works as a low_active borrow.

Downside is, that we still are using a binary adder

inside our schematic, so we have to correct the adder

output if the result is greater than 9...

but we are talking about this later.

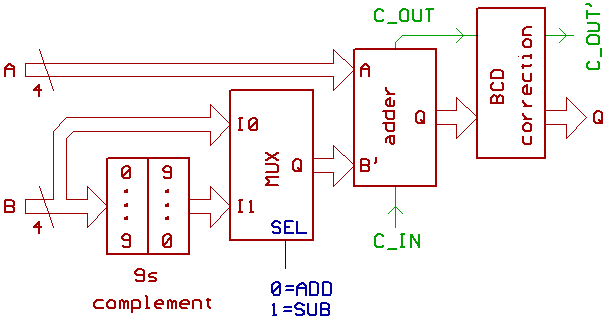

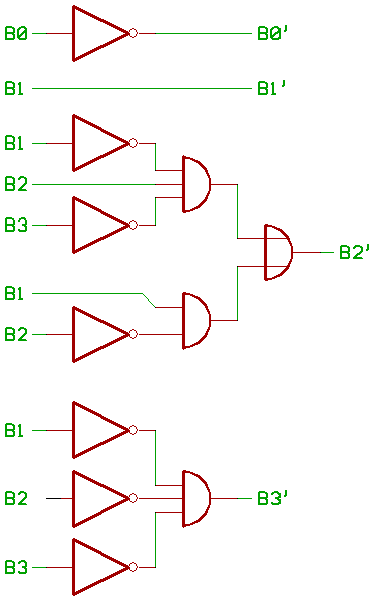

Now a look inside the box labeled "9s complement".

From the truth table above, four inverters won't do this time.

Here an example, of how the 9s complement was generated

inside the Wang 700 calculator:

For better readability of the schematic, I did draw an

AND OR combination gate generating B2'.

The Wang actually does this with NAND gates.

On the next page, I'll show a few more schematics

for generating a 9s complement.

[HOME] [UP]/ [BACK] [1] [2] [3] [4] [5] [6] [7] [8] [NEXT]

(c) Dieter Mueller 2012