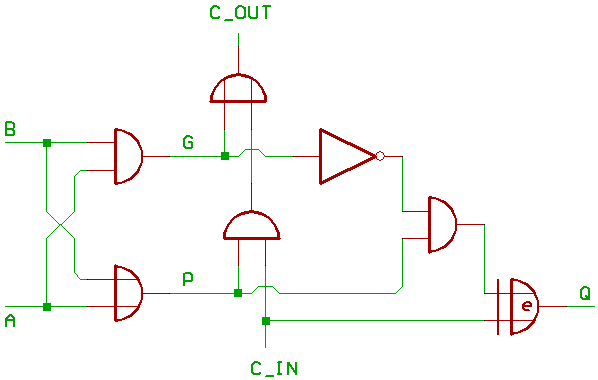

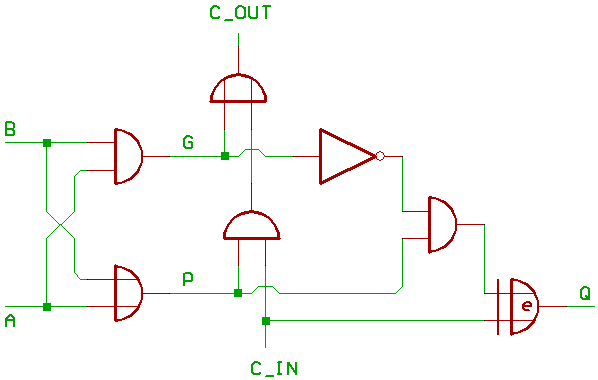

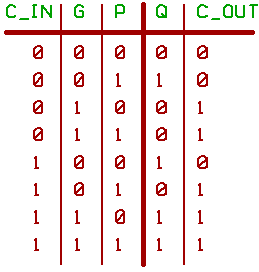

A simple 1 Bit binary full adder with ripple carry.

Not much to say.

If A=1 or B=1, Carry C_IN is propagated (P=1) to C_OUT.

If A=1 and B=1, a Carry is generated (G=1), setting C_OUT to 1.

When A=1 or B=1, but not both of them, and C_IN=0, Q=1.

Q gets inverted, if C_IN=1.

Now to optimize for speed and size.

For more speed, we could use two 74151, both of them

connected to C_IN, A, B at the select lines.

One generates Q, the other C_OUT.

If we draw the multiplexers at gate level,

and optimize for size, the result

may look a bit like the obsolete 7483.

Connecting four 1 Bit adders together:

Unfortunately, carry has to pass through a lot of gates.

For a faster speed, we have to use parallel carry, as in the 74283.

We just take P0..3 and G0..3 from the AND/OR gates

(that are connected to A0..3, B0..3)

Then we calculate C0..3 and give it to the circuitry

that is responsible for Q0..3.

To make things simpler, we call C_IN C0, an C_OUT C4.

C1 = G0 | C0 & P0 C2 = G1 | C0 & P0 & P1 | G0 & P1 C3 = G2 | C0 & P0 & P1 & P2 | G0 & P1 & P2 | G1 & P2 C4 = G3 | C0 & P0 & P1 & P2 & P3 | G0 & P1 & P2 & P3 | G1 & P2 & P3 | G2 & P3

You should recognize some kind of pattern in there.

And if we have low_active P0..3 and G0..3 signals,

and add a P and G output for cascading this structure

to multible lengths of 4 Bit, it is called a 74182.

What, if 74283 and 74182 are no longer available

for the mere hobbyist ?

Time for another 74151 8:1 Multiplexer trick.

We are not limited to three inputs when evaluating

logic functions on the 74151, because it has a low_active

output enable.

Also, who said that the lookup table has to be

only made up with constants ?

A carry chain for 2 Bits, consisting of two AND/OR gate,

to be crammed into one 74151.

Note, that carry_in is low_active, because we have

to abuse the low_active output enable as OR_term.

And now an example how to use it.

Note, that 74151 has two outputs:

one inverted, the other non_inverted.

Could be three times faster than the NAND version,

but not quite as fast as the 74F182/74S182.

Done with dissecting the Adder.

One question comes to mind:

we have an ALU, built around an Adder.

Can we modify the adder structure to form a faster ALU ?

Yes, certainly, we can.

[HOME] [UP]/ [BACK] [1] [2] [3] [4] [5] [6] [7] [8] [NEXT]

(c) Dieter Mueller 2004