|

I2C assembly source. By Lee Davison. |

|

This is the code that drives the I2C bus on the dart control board. The routine Getadrak is to allow access to the bus via the USR() function in EhBASIC.

An example of it's use can be found here.

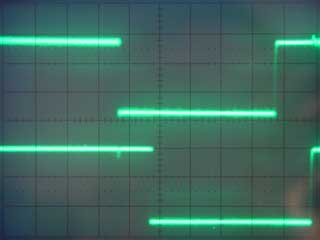

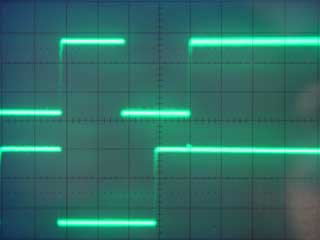

I2C Waveforms.

| Last page update: 4th May, 2004. | e-mail me

|