The ALU (arithmetic logic unit) represents the state of knowledge,

that I had at the end of the year 2004.

For details, consult the last page of my first ALU article.

After building/testing the ALU modules, I figured out that some of

the circuitry isn't needed, and that it would be possible to build the

ALU modules about 30 percent smaller...

So I decided to describe the newer/smaller version.

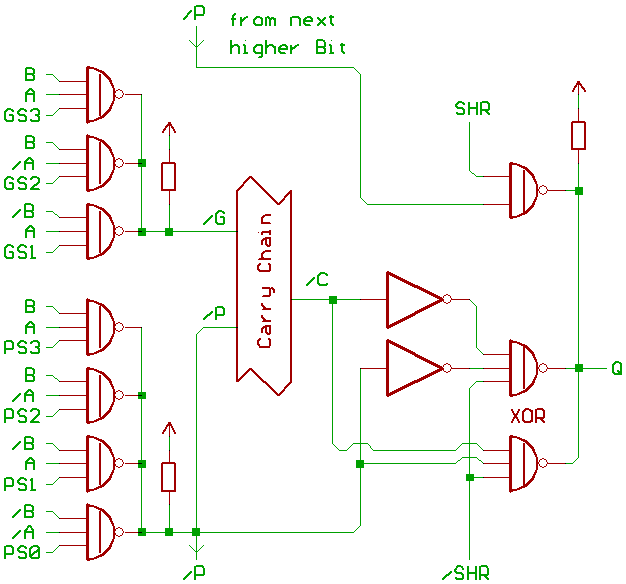

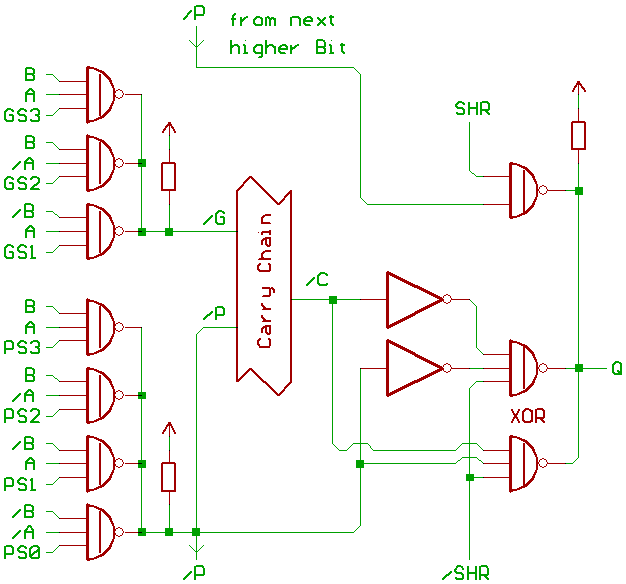

MT15 ALU uses Bitslice modules, one module processes one Bit.

ALU A_input is connected to ACC, PC output.

ALU B_input is connected to data bus.

First stage basically consists of two 4:1 multiplexers,

working as configurable logic gates.

(Two inverters for negating A, B not shown).

It produces the low_active propagate/generate signals.

Imagine this part as a 74153 with inverted outputs.

Propagate means, the carry input should be propagated

through to the next higher ALU Bitslice module.

Generate indicates an overflow, setting the output carry

active to be passed to the next higher Bit.

Since I didn't knew, if my carry circuitry would work

as expected, I decided to make the high and low active

propagate/generate_signals available outside the ALU

Bitslice module.

The inverter for producing the high active generate_signal

isn't shown in this schematic, and could probably be

removed/eliminated.

To be on the safe side, I decided to make the input/output

of the red marked carry inverter available outside the ALU modules,

as well as the inverted/non_inverted carry inputs for the last ALU

stage.

What makes it possible, to wire up the ALU modules to a low active

or high active carry signal, without any further modifications.

The next stage (carry chain) is described at the next page of this article.

Last stage is, basically, an XOR gate, working as a half_adder.

Plus another gate, that takes over during ALU shift right.

For more details, please read my two articles about ALU design.

Now the control signals for some ALU operations:

SHR=1, !SHR=0, shift right:

GS:321 PS:3210

||| ||||

000 1010 shift right register

000 1100 shift right memory

For all other arithmetic/logic functions:

SHR=0, !SHR=1, anything but shift right:

GS:321 PS:3210

||| ||||

101 0000 shift left register

110 0000 shift left memory

000 0000 zero

000 1111 $FFFF

000 1010 pass through register

000 1100 pass through memory

000 1000 register AND memory

000 0110 register XOR memory

000 1110 register OR memory

100 0110 register + memory

001 1001 register - memory

110 0011 memory -1

Incrementing register/memory is a pass_through with the ALU

carry_input forced active.

GS0 was 0 for all ALU functions that made sense, so it was removed.

Again, for more details/functions, please read the articles about ALU design.

[HOME] [UP]/ [BACK] [1] [2] [3] [4] [5] [6] [7] [8] [NEXT]

(c) Dieter Mueller 2005