Imagine, that you would try to build an

ALU with the basic functionality

AND, OR, XOR, ADD.

You may need some additional circuitry

outside the ALU:

All those things already went explained in my

previous articles about ALU design, so we now

skip this part.

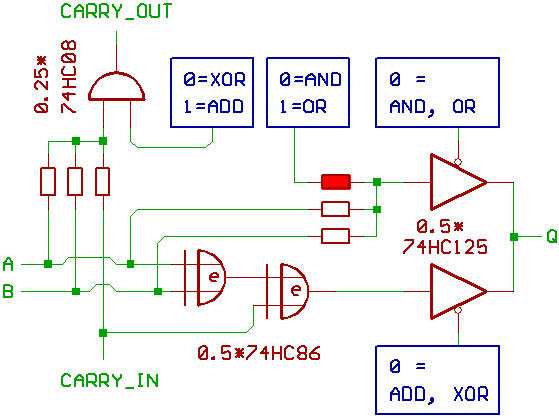

Here a schematic for one Bitslice of the ALU:

The blue boxes connect to the control signals.

The carry chain is built with a majority gate

based on a CMOS AND.

To change the functionality from ADD to XOR,

the carry chain is simply turned off, reducing

the three_input XOR gate (built from two 2_input

XOR gates) of the full adder to a simple 2_input

XOR gate fed from the ALU inputs A and B.

Our ALU has a three state output, so the

output of said XOR is buffered with a 74HC125

(...or 74HC245).

For the AND/OR functionality, there is another

majority gate which can be configurated to work

as an AND/OR gate.

To simplify things, we just took another buffer.

Warning:

be aware of the current which the inputs of your

majority gates will sink/source.

The red marked resistor would be going to be a

problem if you go for speed and low resistor

values.

It may be a good idea to place a buffer in

front of the resistor for every Bitslice of

the ALU.

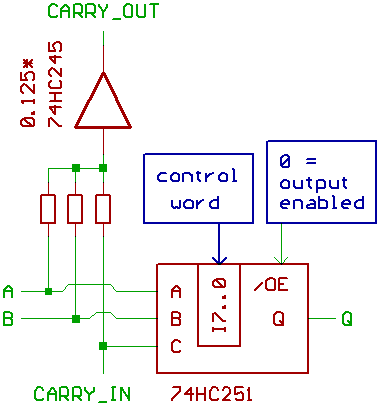

Now for another idea:

A 74HC/AC245 will give a very compact 8 Bit

carry chain.

The rest of the functionality is hidden

inside the 74251 8:1 multiplexer...

which, by the way, has a LOW active output enable.

The select inputs A,B,C of the multiplexer

are tied to the ALU inputs: A,B and carry input.

The functionality of the multiplexer is set by the

data inputs I7..0, which now work as control

lines (MSB first):

AND: 10001000 OR : 11101110 XOR: 01100110 ADD: 10010110

Downside is, that generating the control signals

may require a few additional logic gates.

By the way: when setting the control word to

10101010, the ALU will pass through the input A,

11001100 will pass through the ALU input B.

For more details, please consult/dissect my

previous articles about using multiplexers

for ALU design.

Now for some more boring theory...

[HOME] [UP]/ [BACK] [1] [2] [3] [4] [5] [6] [7] [8] [NEXT]

(c) Dieter Mueller 2009