Written by: Yang / Goodman / Mathys Revision: 1.1 Date Released: 10-MAY-82

This document is submitted with the understanding that it contains information which is confidential in nature and is not to be revealed to anyone without written permission from MOS Technology, Inc.

# Revision History

| Rev ŧ | Date     | Description of Revision                                                              |

|-------|----------|--------------------------------------------------------------------------------------|

|       |          |                                                                                      |

| 0.0   | 2-0ct-81 | Original release                                                                     |

| 1.0   | 1-MAY-82 | General clean-up and reorganization.<br>Rewrite of software architecture description |

•

\*\*\*\*\*\*\*CONFIDENTIAL, MOS TECHNOLOGY, INC. \*\*\*\*\*\*\*\* Page- 2

.

Table of Contents

| 1.0 Introduction                                | 12 |

|-------------------------------------------------|----|

| 1.1 Review of Project Goals,                    | 12 |

| 1.2 Summary of MCS65E4 Capabilities             | 13 |

| 1.3 Terminology                                 | 14 |

| 1.3.1 Introduction                              | 14 |

| 1.3.2 Frocess                                   | 14 |

| 1.3.3 Op Code                                   | 15 |

| 1.3.4 Operand                                   | 15 |

| 1.3.5 Instruction                               | 15 |

| 1.3.6 Descriptor                                | 15 |

| 1.3.7 Ordinal                                   | 16 |

| 1.3.8 Static Data, Dynamic Data,                | 16 |

| 1.3.9 Physical Address                          | 16 |

| 1.3.10 Logical Address                          | 16 |

| 1,3,11 Page Address,                            | 17 |

| 1.3.12 Offset Address, Relative Address,        | 17 |

| 1.4 Example of Addressing in the MCS65E4 System | 20 |

| 2.0 Description of the MCS65E4 Fin Functions    | 22 |

| 2.1 Introduction                                | 22 |

| 2.2 Address Bus Middle / Address Bus Low        | 22 |

| 2.3 Address Bus / Data Bus / Bus Status         | 22 |

| 2.3.1 Interrupt Acknowledge                     | 23 |

| 2.3.2 Hold Acknowledse                          | 23 |

| 2.3.3 Last Instruction Cycle                    | 23 |

| 2.3.4 I/O Reset                                 | 23 |

| 2.3.5 Processor Instruction Fetch               | 23 |

| 2.3.6 Frocessor Data Fetch                      | 23 |

|                                                 |    |

\*\*\*\*\*\*\*CONFIDENTIAL, MOS TECHNOLOGY,INC.\*\*\*\*\*\*\*\* Page- 3

| 2.3.7 Refresh Cucle          | • •  | • •        | • • | • • | • • | ٠   | ÷ +     | • | 24 |

|------------------------------|------|------------|-----|-----|-----|-----|---------|---|----|

| 2.3.8 External Microcode Fe  | etch | • •        | • • | • • | • • | ÷   | • •     | • | 24 |

| 2.4 Row Address Strobe       |      | • •        |     |     | • • | •   |         | • | 24 |

| 2.5 Column Address Strobe    |      | • •        |     | • • |     | •   | • •     | • | 24 |

| 2.6 Chip Power               |      |            | • • |     |     |     | • •     | • | 24 |

| 2.7 Oscillator               |      | • •        |     | • • |     | •   |         | • | 24 |

| 2.8 Bus Clock                |      | • •        |     | • • |     | •   | • •     | • | 24 |

| 2.9 Valid Memory Address     |      |            |     | • • |     |     | • •     | • | 24 |

| 2.10 Memory Ready            |      |            |     |     |     |     |         |   | 25 |

| 2.10.1 Read Cycle,           |      |            |     |     |     |     |         |   | 25 |

| 2.10.2 Write Cycle           |      |            |     |     |     |     |         |   | 25 |

| 2.11 Interrupt Input         |      |            |     |     |     |     |         |   | 25 |

|                              | 3    |            |     |     |     |     |         |   | 25 |

| 2.12 Reset                   |      |            |     |     |     |     |         | • | 26 |

| 2.13 Write Enables           |      |            |     |     |     | •   |         | • |    |

| 2.14 Bus Error               |      |            |     | • • | • • | •   | • •     | • | 26 |

| 2.15 Hold                    | • •  | ••         | • • | * * | • • | •   | • •     | * | 26 |

| 2.16 Instruction Intercept . | • •  | • •        | • • | • • | • • | •   | • •     | • | 26 |

| 3.0 Internal Architecture    | • •  | • •        | • • | • • | • • | •   | • •     | • | 27 |

| 3.1 Introduction             | • •  | • •        | • • | • • | + • | •   | • •     | • | 27 |

| 3.2 Execution Unit           | • •  | • •        | • • | • • | • • | • • | • •     | ٠ | 27 |

| 3.2.1 ABL/ABM Resisters      | • •  | • •        | • • | • • | • • | •   | • { - • | • | 27 |

| 3.2.2 Register Array         | • •  | • •        | • • | • • | •   | • • | • •     | • | 27 |

| 3.2.3 Arithmetic Logic Uni   | t    | • •        | • • | • • | •   | •   | • •     | • | 28 |

| 3.2.4 Input Queue            | • •  | • •        | • • | • • | •   | • • | • •     | • | 28 |

| 3.2.5 ABH/DB Resisters       | • •  | <b>، ،</b> | ۰ ۰ | • • | •   | • • | • •     | ٠ | 28 |

| 3.3 Execution Control Losic. | • •  | * *        | • • | • • | •   | • • | • •     | ٠ | 28 |

| 3.3.1 Control Registers      | • •  | • •        | • • | • • | •   | • • | •••     | • | 28 |

| 3.3.2 Microcode Array        | • •  | • •        | • • | • • | •   | • • | • •     | • | 28 |

|                              |      |            |     |     |     |     |         |   |    |

\*\*\*\*\*\*\*CONFIDENTIAL, MOS TECHNOLOGY, INC. \*\*\*\*\*\*\*\*

Fase- 4

| 4.0 Software Architecture,             | 30 |

|----------------------------------------|----|

| 4.1 Introduction                       | 30 |

| 4.2 Internal Architecture              | 30 |

| 4.2.1 Introduction                     | 30 |

| 4.2.2 Process Base Register            | 30 |

| 4.2.3 Process Limit Register           | 31 |

| 4.2.4 Process Program Counter          | 31 |

| 4.2.5 Primary Base Register            | 31 |

| 4.2.6 Top-of-Stack Register            | 31 |

| 4.2.7 Process Control Register         | 31 |

| 4.2.7.1 Kernal Mode Flag               | 32 |

| 4.2.7.2 User/Supervisor Mode           | 32 |

| 4.2.7.3 Interrupt Inhibit Flag         | 32 |

| 4.2.7.4 Enable External Memory Refresh | 32 |

| 4,2,7,5 Enable Periodic Trap           | 32 |

| 4.2.7.6 Enable Stack Boundary Check    | 32 |

| 4.2.7.7 Debus Mode                     | 32 |

| 4.2.7.8 Enable Read before Byte Write  | 32 |

| 4.2.7.9 Microcode Select               | 33 |

| 4.2.7.10 Refresh Rate                  | 33 |

| 4.3 Process Structure                  | 35 |

| 4.3.1 Introduction                     | 35 |

| 4.3.2 Inter-process Controls           | 35 |

| 4.3.3 Global Data,                     | 35 |

| 4.3.4 Static Data                      | 35 |

| 4.3.5 Dynamic Memory                   | 36 |

| 4.3.5.1 Dynamic Data                   | 36 |

| 4.3.5.2 Free Memory                    | 36 |

|                                        |    |

\*\*\*\*\*\*\*CONFIDENTIAL, MOS TECHNOLOGY,INC.\*\*\*\*\*\*\*\* Page- 5

| 4.3.5.3 Process Stack                                     | •          | ٠ | ÷  | *     | 36  |

|-----------------------------------------------------------|------------|---|----|-------|-----|

| 4.3.6 Frocess Software                                    | •          | • | ٠  | •     | 36  |

| 4.3.7 Frocess Vectors                                     | •          | ÷ | •  | •     | 36  |

| 4.3.8 Kernel Reset Vector                                 | •          | ٠ | •  | •     | 36  |

| 4.4 Execution of Processes in the MCS65E4                 | •          | ٠ | ٠  | •     | 37  |

| 4.4.1 Introduction                                        | •          | • | •  | •     | 37  |

| 4.4.2 Basic Inter-process Controls                        | •          | ٠ | •  | •     | 37  |

| 4.4.2.1 Introduction                                      | •          | • | •  | ٠     | 37  |

| 4.4.2.2 Kernel Reset Vector                               | •          | ٠ | •  | •     | 37  |

| 4.4.2.3 Process Parameter List                            | •          | ٠ | •  | •     | 37  |

| 4.4.2.4 Pointer to current Caller                         | •          | • | ٠  | ٠     | 38  |

| 4.4.2.5 Process Link                                      | •          | • | ٠  | •     | 38  |

| 4.4.2.6 Process Stack                                     | <b>,</b> . | ٠ | ٠  | •     | 39  |

| 4.4.3 Inter-Process Operations                            | •          | • | •  | •     | 39  |

| 4.4.3.1 Introduction                                      | , ,        | • | ٠  | •     | 39  |

| 4.4.3.2 System reset                                      | •          | • | ٠  | •     | 39  |

| 4,4,3,3 Invoking Additional Processes,                    |            | • | •  | •     | 40  |

| 4.4.3.4 Exception Processing                              | , .        | • | •  | •     | 42  |

| 4.4.3.4.1 Introduction                                    | . /        | • | •  | •     | 42  |

| 4.4.3.4.2 Servicing exceptions within the                 |            |   |    |       |     |

| current process                                           | , ,        | • | ×. | •     | 42  |

| 4.4.3.4.3 Servicing exceptions within the calling process | •          | ÷ | •  | •     | 45  |

| 4.4.3.5 Returning to a Suspended Process                  | , ,        | • | ٠  | •     | 45  |

| 4.4.4 Exception Vectors within the                        |            |   |    |       | 4 7 |

| MCS65E4 Process                                           |            |   |    |       | 47  |

| 4.4.4.1 Introduction                                      |            |   |    |       | 47  |

| 4.4.4.2 Undefined Op Code Trap                            |            |   |    |       | 48  |

| 4.4.4.3 Undefined Data Type Trap                          |            |   |    |       | 48  |

| 4.4.4.4 Subscript out-of-limits Trap                      |            | • |    |       | 48  |

| *******CONFIDENTIAL, MOS TECHNOLOGY, INC. ********        |            |   |    | Page- | . 6 |

| 4.4.4.5 Operator and Operand Not Compatible,         | • | + | ٠ | •     | 48  |

|------------------------------------------------------|---|---|---|-------|-----|

| 4.4.4.6 Overflow                                     | ÷ | • | ٠ | *     | 48  |

| 4.4.4.7 Other Arithmetic Error                       | ٠ | ٠ | ٠ | •     | 48  |

| 4.4.4.8 Non-conformable Data Types                   | + | ٠ | ٠ | •     | 48  |

| 4.4.4.9 Instruction Access Trap                      | • | ٠ | • | •     | 49  |

| 4,4,4,10 Data Access Trap                            | • | ٠ | ٠ | ٠     | 49  |

| 4.4.4.11 Frocess Stack Page Boundary Trap            | ٠ | ٠ | ٠ | •     | 49  |

| 4.4.4.12 Debus Trap                                  | • | • | ٠ | •     | 49  |

| 4,4,4,13 Interrupt Input                             | ٠ | ٠ | ٠ | •     | 49  |

| 4.4.4.14 System Call                                 | • | • | ٠ | ٠     | 49  |

| 4.4.4.15 System Call with Message                    | • | ٠ | • | •     | 49  |

| 4.4.4.16 Bus Error                                   | • | ٠ | ٠ | •     | 49  |

| 4.4.4.17 Access out-of-limit                         | ٠ | ٠ | • | •     | 49  |

| 4.5 Addressing within the MCS65E4                    | ٠ | ٠ | • | ٠     | 50  |

| 4.5.1 Introduction                                   | ٠ | • | • | •     | 50  |

| 4.5.2 Primary Addressing Group                       | • | • | • | •     | 53  |

| 4.5.2.1 Introduction                                 | • | • | • | •     | 53  |

| 4.5.2.2 Base Register Select Field                   | • | • | • | •     | 53  |

| 4.5.2.3 Data Access Format                           | ٠ | • | ٠ | ٠     | 53  |

| 4.5.2.4 Number of Extension Bytes                    | • | ٠ | • | •     | 54  |

| 4.5.3 Secondary Addressing Group                     | • | • | • | ٠     | 54  |

| 4.5.3.1 Introduction                                 | ٠ | • | • | •     | 55  |

| 4,5,3,2 Limit Page Addressing                        | • | • | • | •     | 55  |

| 4.5.3.3 Process Stack PUSH / POP ,                   | • | • | ٠ | •     | 55  |

| 4.5.3.4 Immediate Addressing, Long Form,             | • | • | • | •     | 50  |

| 4.5.4 Internal Register Addressing                   | • | ٠ | • | ٠     | 50  |

| 4.5.5 Immediate Addressing, Short Form               | • | • | ٠ | •     | 60  |

| 4.5.6 Process Base Addressing, Short Form            | • | • | + | •     | 61  |

| ********CONFIDENTIAL, MOS TECHNOLOGY, INC. ********* |   |   |   | Fase- | - 7 |

$\left| \left( \begin{array}{c} 1 & 1 \\ 1 & 2 \end{array} \right) + \left( \begin{array}{c} 1 & 2 \\ 2 \end{array} \right) + \left( \begin{array}{c} 1 & 2 \end{array} \right) + \left( \begin{array}{c} 1 & 2 \\ 2 \end{array} \right) + \left( \begin{array}{c} 1 & 2 \end{array} \right) + \left( \begin{array}{c} 1$

.

| 4.5.7 Primary Base Addressing, Short Form      | ٠   | ٠ | ٠ | • | + | 61         |

|------------------------------------------------|-----|---|---|---|---|------------|

| 4.6 Data Structure Within the MCS65E4 System . | •   | ۷ | ٠ | • | ٠ | 53         |

| 4.6.1 Introduction                             | •   | • | + | ٠ | + | 63         |

| 4,6,2 The Basic Data Elements, , , , , , , ,   | ÷   | ٠ | • | • | • | 66         |

| 4.6.2.1 Unsigned Binary Data Fields,           | ٠   | * | ٠ | ÷ | • | 55         |

| 4.6.2.2 Signed Binary Data Fields              | •   | ٠ | ٠ | • | • | 65         |

| 4.6.2.3 BCD Data Fields                        | ٠   | ٠ | ٠ | ٠ | • | <b>6</b> 6 |

| 4.6.2.4 Floating Point Data Fields             | •   | ٠ | ٠ | • | • | 65         |

| 4.6.2.5 String Data Fields                     | ٠   | ٠ | ٠ | • | • | 66         |

| 4.6.3 Organization of the Variable Descripto:  | r . | ٠ | ٠ | ٠ | • | 33         |

| 4.6.3.1 Introduction                           | •   | ٠ | ٠ | • | • | 63         |

| 4.6.3.2 Organization of the Descriptor         |     |   |   |   |   |            |

| Header                                         | •   | • | • | • | • | 38         |

| 4.6.3.2.1 Introduction                         | •   | ٠ | • | • | • | 68         |

| 4.6.3.2.2 Trap Bit                             | •   | ٠ | • | ٠ | • | 38         |

| 4.6.3.2.3 Access Mode                          | ٠   | ٠ | • | ٠ | • | 68         |

| 4.6.3.2.3.1 Attached                           | •   | • | • | ٠ | • | 69         |

| 4.6.3.2.3.2 Attached Relocatable               | ٠   | • | • | ٠ | • | 69         |

| 4.6.3.2.3.3 Short Relative                     | ٠   | • | • | ٠ | • | 69         |

| 4.6.3.2.3.4 Short Relocatable                  | •   | • | • | • | • | 59         |

| 4.6.3.2.3.5 Long Relative                      | ٠   | ٠ | ٠ | ¢ | • | 69         |

| 4.6.3.2.3.6 Long Relocatable                   | •   | ٠ | • | ٠ | • | 70         |

| 4.6.3.2.3.7 Logical Addressing                 | •   | ٠ | • | • | • | 70         |

| 4.6.3.2.4 Data Type Field and Flag             | ٠   | ٠ | ٠ | ٠ | • | 70         |

| 4.6.4 The Data Structures                      | ٠   | ٠ | ٠ | ٠ | ٠ | 74         |

| 4.6.4.1 Introduction                           | ٠   | ٠ | ٠ | ٠ | ٠ | 74         |

| 4.6.4.2 Single Dimension Arrays                | •   | • | ٠ | • | • | 74         |

| 4.6.4.3 Array Structure                        | ٠   | ٠ | ٠ | ٠ | • | 77         |

\*\*\*\*\*\*\*CONFIDENTIAL, MOS TECHNOLOGY,INC.\*\*\*\*\*\*\*\* Pase- 8

8

,

| 4.6.4.4 Record                                                | + +        | •    | 82        |

|---------------------------------------------------------------|------------|------|-----------|

| 4.6.5 Deferred Descriptor,                                    | • •        | *    | 36        |

| 4.6.6 Application of the MCS65E4 Data<br>Accessing Mechanisms |            |      | 88        |

|                                                               |            |      |           |

| 4.6.6.1 Introduction                                          | •          | •    | 88        |

| 4.6.6.2 Accessing Data in Multi-Dimensional<br>Arrays         |            | ٠    | 88        |

| 4.6.6.3 Example of Accessing a multi-dimensional array        |            |      | 94        |

| 4.6.6.4 Example of Accessing Data in a Complex                | ·          | ·    |           |

| Record Structure,                                             | •          | •    | 99        |

| 4.6.6.5 Exception Vectors                                     | •          | ٠    | 104       |

| 4.6.6.5.1 Introduction                                        |            | •    | 104       |

| 4.6.6.5.2 Descriptor Format                                   | , <b>.</b> | •    | 104       |

| 4.6.6.5.3 Example of Attached Address<br>Descriptor Format    |            |      | 105       |

|                                                               |            |      |           |

| 4.6.5.4 Example of Remote Exception Vector .                  |            |      | 105       |

| 4.7 The MCS65E4 Instruction Set                               |            |      | 107       |

| 4.7.1 Introduction                                            |            |      | 107       |

| 4.7.2 Format of the MCS65E4 Op Codes                          | *          | •    | 107       |

| 4.7.3 Basic Arithmetic and Logic Operations,                  | •          | •    | 109       |

| 4.7.3.1 Introduction                                          | ٠          | •    | 109       |

| 4.7.3.2 ADD                                                   | •          | •    | 111       |

| 4.7.3.3 SUBTRACT                                              | •          | •    | 112       |

| 4.7.3.4 MUL                                                   | •          | ٠    | 113       |

| 4.7.3.5 DIVIDE                                                | •          | ٠    | 114       |

| 4.7.3.6 AND                                                   | •          | •    | 115       |

| 4.7.3.7 OR                                                    | •          | ٠    | 117       |

| 4.7.3.8 EOR                                                   | •          | ٠    | 119       |

| 4.7.3.9 MOD                                                   | •          | •    | 121       |

| 4.7.3.10 ABS                                                  | ٠          | •    | 122       |

| ********CONFIDENTIAL, MOS TECHNOLOGY,INC.********             |            | Pa⊴e | <b></b> 9 |

and the second se

|                   | _      |      |     |     |     |            |    |     |     |    |     |    |    |          |    |   |   |   |       |       |

|-------------------|--------|------|-----|-----|-----|------------|----|-----|-----|----|-----|----|----|----------|----|---|---|---|-------|-------|

| 4.7.4.11 NE       |        |      |     |     |     |            |    |     |     |    |     |    |    |          |    |   |   |   |       | 123   |

| 4.7.3.12 IN       | C      | • •  | ٠   | +   | +   | +          | ٠  | ٠   | •   | ٠  | ٠   | •  | ٠  | ٠        | +  | ٠ | • | ٠ | ٠     | 124   |

| 4.7.3.13 DE       | С,     | • •  | ٠   | ٠   | ٠   | ٠          | ٠  | •   | •   | •  | ٠   | ٠  | ٠  | ٠        | ٠  | ٠ | • | ٠ | •     | 125   |

| 4.7.3.14 SQ       | RT.    | • •  | •   | ٠   | ٠   | •          | •  | ٠   | ٠   | •  | •   | •  | ٠  | •        | ٠  | ٠ | ٠ | • | •     | 126   |

| 4.7.3.15 MO       | V .    | • •  | ٠   | ٠   | ٠   | ٠          | ٠  | ٠   | ٠   | •  | ٠   | ٠  | ٠  | ٠        | ٠  | ٠ | ٠ | ٠ | •     | 127   |

| 4.7.3.16 LE       | AUZ    | • •  | •   | ٠   | ٠   | ٠          | ٠  | ٠   | •   | ٠  | ٠   | ٠  | •  | •        | ٠  | ٠ | ٠ | ٠ | ٠     | 128   |

| 4.7.3.17 LE       | AD1    | • •  | ٠   | ٠   | •   | •          | •  | ٠   | •   | ٠  | ٠   | ٠  | •  | •        | •  | ٠ | ٠ | ٠ | ٠     | 129   |

| 4.7.3.18 CL       | R •    | • •  | ٠   | ٠   | ٠   | ٠          | ٠  | ٠   | ٠   | ٠  | •   | •  | •  | ٠        | ٠  | • | ٠ | ٠ | ٠     | 130   |

| 4.7.3.19 SE       | т.     | • •  | ٠   | ٠   | ٠   | ٠          | •  | ٠   | ٠   | ٠  | •   | ٠  | ٠  | ٠        | •  | ٠ | ٠ | ٠ | ٠     | 131   |

| 4.7.4 Frogram     | Cont   | tro  | 1 ] | Ins | itr | יי<br>ט ני | ti | on  | s   | •  | •   | •  | •  | ٠        | ٠  | • | ٠ | ٠ | ٠     | 132   |

| 4.7.4.1 Int       | rodu   | cti) | on  | ٠   | •   | •          | •  | ٠   | •   | ٠  | •   | •  | •  | •        | •  | • | • | ٠ | ٠     | 132   |

| 4.7.4.2 BEQ       | • • •  | • •  | •   | •   | ٠   | •          | ٠  | ٠   | •   | •  | •   | ٠  | •  | •        | ٠  | • | • | ٠ | •     | 133   |

| 4.7.4.3 BNE       | • •    | • •  | ٠   | •   | ٠   | •          | ٠  | ٠   | •   | ٠  | •   | •  | •  | ٠        | •  | • | ٠ | ٠ | •     | 134   |

| 4.7.4.4 BGT       | • • •  | ••   | ٠   | ٠   | •   | •          | •  | ٠   | ٠   | ٠  | ٠   | •  | •  | ٠        | ٠  | • | ٠ | ٠ | •     | 135   |

| 4.7.4.5 BGE       | • • •  | • •  | •   | •   | •   | •          | •  | ٠   | ٠   | •  | •   | •  | •  | •        | •  | ٠ | ٠ | • | ٠     | 136   |

| 4.7.4.6 BEQ       | Ζ.     | •••  | •   | ٠   | ٠   | ٠          | ٠  | •   | ٠   | •  | •   | ٠  | •  | •        | ٠  | • | ٠ | ٠ | •     | 137   |

| 4.7.4.7 BNE       | Ζ.     | • •  | •   | •   | •   | •          | •  | ٠   | •   | •  | ٠   | ٠  | ٠  | ٠        | ٠  | ٠ | ÷ | • | ٠     | 138   |

| 4.7.4.8 BFO       | S .    | •••  | ٠   | ٠   | ٠   | •          | •  | ٠   | •   | ٠  | •   | •  | •  | •        | ٠  | • | • | • | ٠     | 139   |

| 4.7.4.9 BMI       | * * •  | • •  | ٠   | ٠   | ٠   | •          | ٠  | •   | •   | •  | •   | •  | •  | ٠        | •  | • | ٠ | ٠ | ٠     | 140   |

| 4.7.4.10 BR       |        | • •  | •   | •   | •   | •          | •  | •   | •   | •  | •   | •  | •  | •        | •  | • | • | • | •     | 141   |

| 4.7.4.11 JM       | Ρ.     | • •  | •   | •   | •   | •          | •  | •   | •   | •  | •   | •  | •  | •        | •  | • | ٠ | • | •     | 142   |

| 4.7.4.12 BS       | R' • • | • •  | •   | •   | •   | •          | •  | •   | •   | •  | •   | •  | •  | •        | ٠  | • | • | ٠ | •     | 144   |

| 4.7.4.13 JS       | R.     | • •  | •   | •   | •   | •          | ٠  | •   | ٠   | •  | •   | •  | •  | 5 4<br>• | •  | + | • | • | •     | 145   |

| 4.7.4.14 BD       |        |      |     |     |     |            |    |     |     |    |     |    |    |          |    |   |   |   |       | 147   |

| 4.7.4.15 BC       | . יואס |      | •   | •   | ٠   | •          | •  | •   | •   | •  | •   | •  | •  | •        | ٠  | • | ٠ | • | •     | 148   |

| 4.7.4.16 SC       | • • •  | • •  | ٠   | •   | •   | •          | •  | •   | •   | •  | ٠   | •  | ٠  | •        | ÷  | • | • | • | •     | 149   |

| 4.7.4.17 SC       | м.     | • •  | •   | •   | •   | •          | •  | •   | •   | •  | •   | •  | •  | •        | •  | • | • | • | •     | 150   |

| 4.7.4.18 RT       | s.,    | • •  | •   | •   | •   | ٠          | •  | +   | •   | •  | ٠   | •  | •  | ٠        | •  | • | • | • | •     | 151   |

| *********CONFIDEN | TIAL   | , M  | DS  | ΤE  | сн  | סאו        | LC | ιGΥ | , I | NC | • * | ** | ** | **       | ** |   |   |   | F'age | e- 10 |

|                   |        |      |     |     |     |            |    |     |     |    |     |    |    |          |    |   |   |   |       |       |

| 4.7.4.1       | 9 RTE   | ٠   | ٠   | ٠   | ٠    | ٠      | ٠  | + | ٠ | ٠ | ٠ | ٠ | ٠ | ٠ | ٠ | ٠ | ٠ | ٠  | • | ٠ | • | 152 |

|---------------|---------|-----|-----|-----|------|--------|----|---|---|---|---|---|---|---|---|---|---|----|---|---|---|-----|

| 4.7.4.20      | D IOS   | ٠   | ٠   | ٠   | ٠    | ٠      | •  | ٠ | ٠ | ٠ | • | ٠ | ٠ | • | + | ٠ | + | •  | ٠ | • | • | 153 |

| 4 . 7 . 4 . 2 | 1 TASH  | ٢.  | ٠   | ٠   | ٠    | •      | •  | ٠ | ٠ | ٠ | ٠ | ٠ | ٠ | ٠ | ٠ | ٠ | ٠ | ٠  | • | ٠ | • | 154 |

| 4.7.5 Adv:    | зпсеб   | Ô۶  | er  | ۰ət | ic   | 0 Г1 9 | 5. | ٠ | ٠ | ٠ | • | ٠ | ٠ | ٠ | ٠ | ٠ | ٠ | ٠  | ٠ | • | • | 155 |

| 4.7.5.1       | Intro   | odu | ıct | ;ic | ) [] | •      | ٠  | ٠ | ٠ | ٠ | ٠ | ٠ | ٠ | • | • | ٠ | ٠ | ٠  | • | ٠ | • | 155 |

| 4.7.5.2       | RESET   | ٢.  | ٠   | ٠   | ۰    | +      | •  | ٠ | ٠ | • | • | • | ٠ | • | • | • | ٠ | ٠  | • | ٠ | ٠ | 156 |

| 4.7.5.3       | CEQ     | ٠   | •   | ٠   | •    | ٠      | ٠  | ٠ | ٠ | ٠ | • | • | ٠ | ٠ | • | ٠ | ٠ | •  | ٠ | ٠ | ٠ | 157 |

| 4.7.5.4       | CNE     | ٠   | •   | ٠   | ٠    | ٠      | ٠  | ٠ | ٠ | • | ٠ | • | ٠ | ٠ | ٠ | ٠ | ٠ | ٠  | ٠ | ٠ | ٠ | 158 |

| 4.7.5.5       | CGT     | ٠   | •   | •   | •    | ٠      | ٠  | ٠ | • | • | ٠ | ٠ | • | ٠ | ٠ | • | • | •  | ٠ | ٠ | • | 159 |

| 4.7.5.6       | CGE     | ٠   | •   | •   | •    | •      | ٠  | ٠ | • | ٠ | ٠ | ٠ | ٠ | ٠ | • | ٠ | • | ٠  | • | • | • | 160 |

| 4.7.5.7       | FIND    | ٠   | ٠   | •   | •    | •      | ٠  | ٠ | • | • | • | • | ٠ | ٠ | • | • | • | •  | • | ٠ | • | 161 |

| 4.7.5.8       | DETC    | ٠   | ٠   | •   | •    | ٠      | •  | ٠ | ٠ | ٠ | ٠ | ٠ | ٠ | ٠ | ٠ | ٠ | ٠ | •  | • | • | • | 163 |

| 4.7.5.9       | NDET    | ٠   | ٠   | ٠   | ٠    | ٠      | ٠  | ٠ | ٠ | ٠ | ٠ | ٠ | • | • | • | • | • | ٠  | ٠ | ٠ | ٠ | 164 |

| 4.7.5.10      | DETR    | ζ.  | ٠   | ٠   | ٠    | ٠      | ٠  | ٠ | ٠ | ٠ | • | ٠ | ٠ | ٠ | • | ٠ | ٠ | ٠  | • | • | • | 167 |

| 4.7.5.11      | SHM     | •   | ٠   | •   | ٠    | ٠      | ٠  | • | • | • | • | ٠ | • | • | ٠ | ٠ | ٠ | ۰. | • | • | • | 169 |

| 4.7.5.12      | 2 PTR   | ٠   | ٠   | ٠   | ٠    | ٠      | •  | • | • | ٠ | • | ٠ | ٠ | ٠ | ٠ | ٠ | ٠ | ٠  | ٠ | ٠ | • | 171 |

| 4.7.5.13      | 5 DITYF | Έ   | ٠   | ٠   | •    | •      | •  | • | ٠ | ٠ | ٠ | • | • | • | • | ٠ | ٠ | •  | ٠ | ٠ | ٠ | 173 |

| 4.7.5.14      | I CNVR  | T   | ٠   | ٠   | ٠    | ٠      | ٠  | ٠ | ٠ | ٠ | • | ٠ | ٠ | • | ٠ | • | ٠ | ٠  | • | ٠ | • | 175 |

| 4.7.5.15      | 5 EVAL  | . • | •   | ٠   | •    | ٠      | •  | • | ٠ | • | • | ٠ | ٠ | • | • | ٠ | • | ٠  | ٠ | ٠ | • | 176 |

|               |         |     |     |     |      |        |    |   |   |   |   |   |   |   |   |   |   |    |   |   |   |     |

# 1.0 Introduction

This specification contains a detailed description of all aspects of the MCS65E4 microprocessor development project, beginning in Section 1 with a review of the project goals and a discussion of the market toward which this chip is directed. It is hoped that these discussions will lead to greater understanding of the goals of the project on the part of everyone involved.

Section 2 contains a description of the MCS65E4 interface. This is followed by a description of the internal architecture of the MCS65E4 (Section 3), including the register organization, the internal buses and the organization of the control store. Section 4 contains a detailed description of the MCS65E4 software architecture (addressing modes, instruction set, etc.).

1.1 Review of MCS65E4 Project Goals

Before entering into a detailed discussion of the MCS65E4, it would be useful to briefly review the major factors which have influenced the design of this processor system. Understanding these factors will be particularly important for anyone involved in the design verification stage of this project.

Although the MCS65E4 is equipped with a "compatible" mode in which it is capable of executing software which was written for the MCS6502, the MCS65E4 is not designed to be upward compatible with the 6502 family of 8-bit microprocessors. The primary reason for this is that the basic design considerations behind the 6502 processor differ greatly from those described below for the MCS65E4 processor. This is true in spite of the fact that the 6502 has reached a dominant position in the microcomputer market, one of the target markets for the MCS65E4.

To put the 6502 architecture into perspective, it should be noted that when this design effort began, microprocessors were viewed primarily as replacements for random logic in the design of controllers. The 6502 was optimized toward this application. To this end, significant emphasis was placed on minimum system configurations and on minimizing device and system cost. This was accomplished through the use of such things as page zero addressing, 8-bit index registers, multiple-function support devices, and generally simplified system interfacing.

Many of the characteristics of the 6502 which were designed to maximize its performance as a random logic replacement would seem to limit its performance in high-end microcomputer systems. In spite of this fact, low cost and ease of use has allowed the 6502 to become a dominant factor in this market. These are the features which will be retained in the MCS65E4. At the same time, the architecture of this "next generation" processor will be designed to assure maximum performance in microcomputer systems at the lowest possible cost.

Modern high-end microcomputer systems exhibit several features which can greatly influence the design of a processor optimized

\*\*\*\*\*\*\*CONFIDENTIAL, MOS TECHNOLOGY,INC.\*\*\*\*\*\*\*\* Pase- 12

for this application. In particular, all such systems are controlled by a sophisticated operating system. In many cases, components of this operating system are swapped into and out of memory as required. Most such systems support several user's programs in a "multi-task" environment, reallocating the available memory from system to user or from one user to another as required.

There are several important problems inherent in this type of system. The first is memory protection. It is important that the operating system be protected from the user's programs and that the user's programs be protected from each other. In addition, the software should be "relocatable" since the physical address space in which the program will be located is generally determined at execution time.

In addition to the above, it is assumed that most microcomputer programming will involve the use of a high-level language. Therefore, the software architecture of the processor must be designed to minimize the time required for both compilation and execution of such languages.

Finally, it should be noted that even the most powerful processor is wasted if it is absorbed in I/O handling a large portion of the time. For this reason, the system level problems of interrupt, DMA, etc. must be handled in a manner which maximizes the amount of time which the processor has available for "computing".

All of these factors have had a strong influence on the design of the MCS65E4. However, the design described below addresses each of these factors in a manner which provides maximum performance within well-defined chip size constraints. The architecture described in this document can be built into a device which will be well within "state of the art", providing a combination of device cost and performance which should allow it to assume the dominant position in the micro- computer market now held by the 6502.

1.2 Summary of MCS65E4 capabilities

The following is a brief listing of the principal features of the MCS65E4 family of microprocessors.

- 1. 8, 16 or 32-bit Data Bus.

- 2. 24-bit Address Bus.

- 3. ALU processes 32 bits of data for each processor cycle.

- No internal data registers visible to the programmer. All operations are "memory-to-memory".

- Internal operand redisters allow processing of multi-byte operands,

and a set of the set o

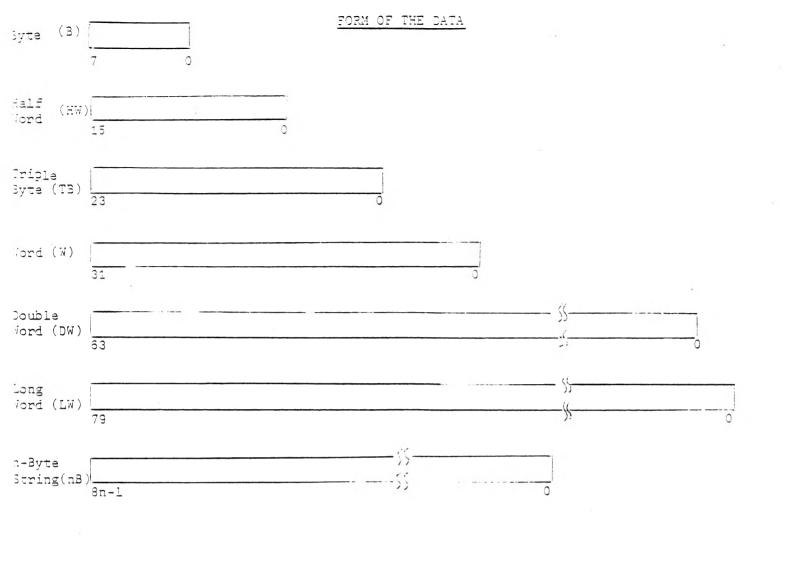

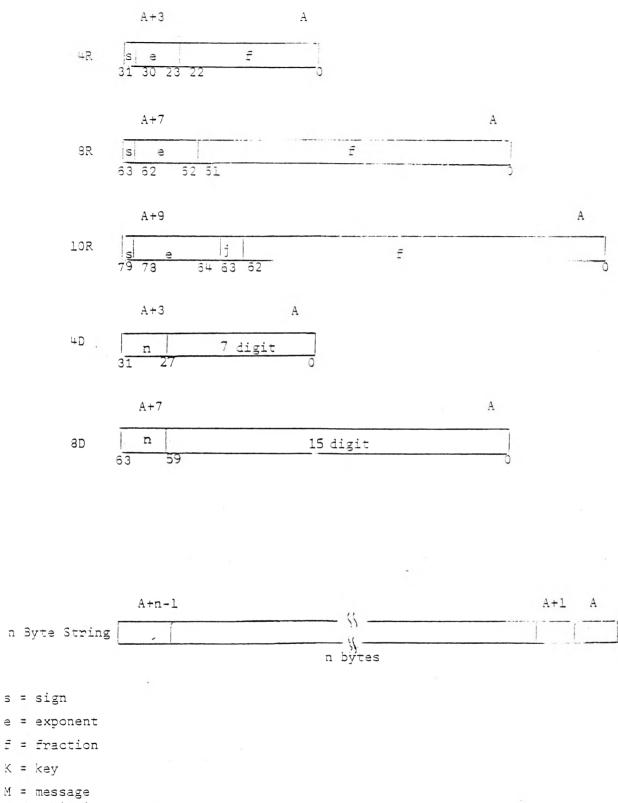

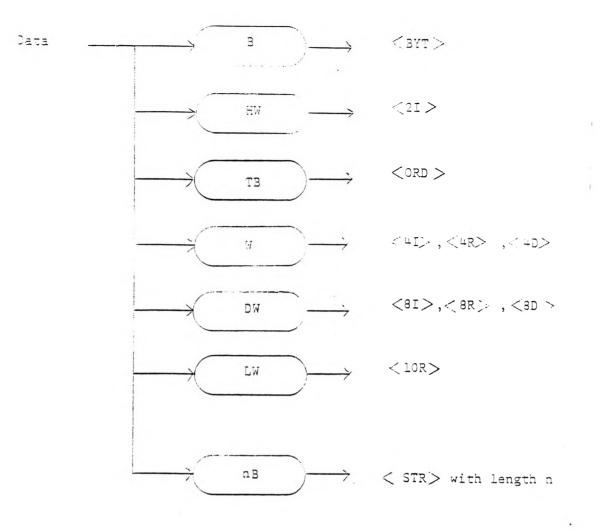

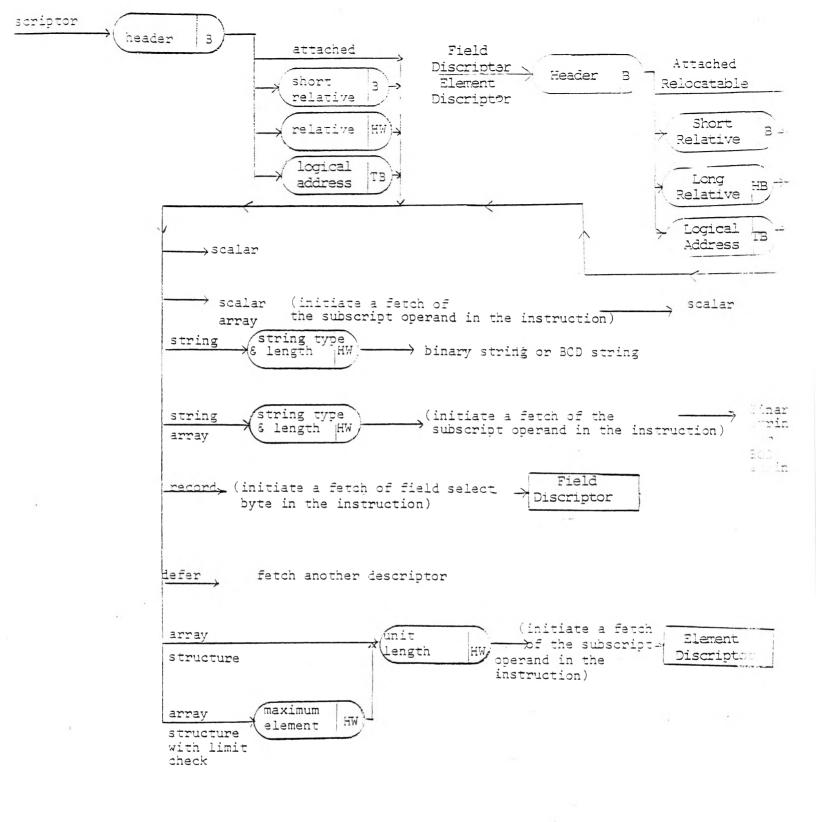

the format of the data fields.

- 7. "Self-defining" data structures, i. e., most data is accessed through tags and descriptors. However, the ability to directly access and manipulate byte, double byte and triple byte fields is provided to facilitate the generation of descriptor and pointer addresses, etc.

- 8. On-chip hardware and microcode support for many operating system functions.

- 9. Hardware support for:

- -s. Error Detection and correction.

- b. Virtual memory.

- c. Prioritized and vectored interrupts.

.

- d. Floating point data types.

- e. Decimal (BCD) data types.

## 1.3 Terminology

### 1.3.1 Introduction

The architecture of the MCS65E4 contains a number of very important concepts which are unique to the world of microprocessors. To assure the accurate transfer of information, therefore, this section introduces what is hopefully a clear, consistent terminology which will be employed throughout this document.

## 1.3.2 Process

and the second second

The 'process' is one of the key concepts in the MCS65E4 architecture. In general, a process can be described as a self-contained combination of software and data. The address limits within which a process must execute are defined by information stored in an internal Process Base Register for the lower limit and in a Process Limit Register for the upper limit. Special hardware within the MCS65E4 assures that a process does not access any memory locations outside of the address space defined by these two registers.

There are several important process characteristics which affect the execution of software within the MCS65E4. The most important is that all processes are totally relocatable, i. e., an MCS65E4 program will execute in exactly the same manner no matter where it is located in the 16 mega-byte address space. In addition, an active process can be suspended, and can be moved within the address space of its caller without affecting subsequent execution.

There are three types of processes within the MCS65E4 architecture. These are the Kernel, the Operating System and the User process. Each exhibits characteristics which reflect its position in a well-defined hierarchy. The term "Kernel process" refers to the lowest level in the set of processes which forms a

\*\*\*\*\*\*\*CONFIDENTIAL, MOS TECHNOLOGY,INC.\*\*\*\*\*\*\*\* Page- 14

complete MCS65E4 system. The processor enters this mode through the chip reset function or through system calls and traps which occur in the higher level processes. Within the Kernel, the processor can call either a higher level operating system process or a User process. These higher levels of operating system can continue to call additional processes until a User process is encountered. This hierarchy of processes is described in detail. below.

Within this specification, the terms "Kernel process" will be used to refer to process level 1 in which both the Kernel flag and the User/Supervisor flag are set. The term "Operating System Process will refer to those higher level processes in which the User/Supervisor flag is set but the Kernel flag is cleared. This can be summarized as follows:

| Process          | Kernel<br>Flag | User/Supervisor<br>Flag |

|------------------|----------------|-------------------------|

| Kernel           | 1              | 1                       |

| Operating System | 0              | 1                       |

| User             | 0              | 0                       |

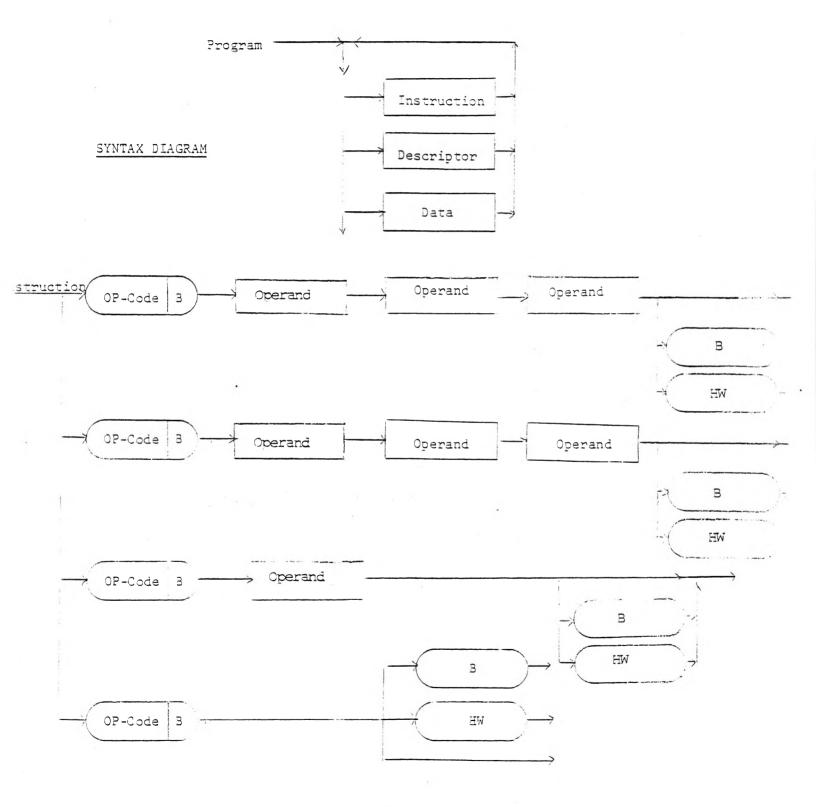

### 1.3.3 Op Code

The term 'OP Code' refers to the first byte of each instruction, This byte specifies the operation to be performed (Add, Subtract, etc.) and the format of the instruction. However, it does not specify the type of the data (Real, BCD, etc.) which is to be manipulated by the instruction.

### 1.3.4 Operand

The term "operand" refers to that portion of the instruction which contains the information necessary to access a single data field. The first byte of the operand specifies the manner in which the desired data field is to be accessed. Specifically, the data can be located in an internal register, it can be in the instruction (immediate data), or it can be accessed through the normal data referencing mechanism described below.

#### 1.3.5 Instruction

The term 'instruction' refers to the combination of OF Code and Operands which are accessed under direct control of the Process Program Counter to cause a complete execution sequence to take place within the processor.

#### 1.3.6 Descriptor

Within the MCS65E4 architecture, the "data descriptor" acts as the primary means by which the processor determines the format and location of a data field. The term descriptor refers to all of the information required to access a data field. The components which

\*\*\*\*\*\*\*CONFIDENTIAL, MOS TECHNOLOGY,INC.\*\*\*\*\*\*\*\*\* Pase- 15

make up a descriptor are:

- 1. Descriptor Header.

- 2. Address Reference Information.

- 3. Auxiliary Information.

The operation of the descriptor is described in detail in Section 4.

1.3.7 Ordinal

The term "ordinal" will be used to refer to the three-byte unsigned binary fields which are used to store logical addresses, offset addresses, etc. within the MCS65E4 architecture.

1.3.8 Static Data, Dynamic Data

During the discussions of process organization and execution within the MCS65E4, the terms static data and dynamic data will be used to differentiate between process variables which retain the same format for the life of the process and those which are created and abolished while the process is being executed. The most important characteristic of these two types of data is that the amount of memory required by the static data will not change during execution of the process. Dynamic data, however, consists of variables which cannot be assigned fixed amounts of memory during compilation of the process software because the memory requirements for these variables will only be known at run time.

1.3.9 Physical Address

The term "physical address" will be used to specify a position in the 16-mesabyte address space which the MCS65E4 can access. These are the addresses which appear on the pins of the processor.

Throughout this document, the physical address is assumed to be the 'default.' Therefore, if an address type (physical, logical, etc.) is not specified, it can be assumed to be a physical address.

1.3.10 Logical Address

------

One of the most important aspects of the stand-alone nature of a process is that all addressing within the process software is self-contained and is completely independent of the physical memory locations in which the process resides. All addresses generated during execution of the process software are assumed to be offsets from the address contained in the Process Base register. For example, if a process whose base address is 044B00 (HEX) were to specify an address of 0177 (HEX), the physical address which would be accessed is 044C77 which is obtained by adding 0177 to 044B00.

This characteristic of addressing within the MCS65E4 brings up the concept of the logical address. In this document, the term logical address will be used to refer to the position of a memory location within the address space of a process. In the above example,

\*\*\*\*\*\*\*CONFIDENTIAL, MOS TECHNOLOGY,INC.\*\*\*\*\*\*\*\* Pase- 16

therefore, the logical address would be 0177. It should be noted that all software execution within the MCS65E4 is performed within the context of a process. For this reason, all memory locations have both a physical and a logical address. The physical address remains fixed by the system logic. However, the logical address of each memory location is entirely a function of its position within a process. This will be illustrated in the example below (See Figure 1.1).

To assure accuracy, this document will utilize the phrase "within process (process name)" whenever a logical address is specified. Also, a memory location which is outside of the limits of a process is assumed to have no logical address within that process, i. e., the logical address is assumed not to exist.

1.3.11 Pase Address

There are many aspects of the MCS65E4 architecture which assume an eight bit organization. For example:

- 1. Op codes are eight bits wide.

- 2. The minimum addressable data field is eight bits wide.

- 3. Offset addresses can be zero, eight, sixteen or 24 bits.

- Both the base and limit for a process are specified in 256-byte increments.

As a result, it will be useful to utilize the term 'Pase address' to identify the location of a 256-byte page. Throughout this document, the Page Address will be specified by the upper 16 address bits with the low order eight bits identified by XX. For example, Page Address 01E4XX identifies the page whose upper sixteen address bits are 01E4. This page includes addresses 01E400 through 01E4FF.

In addition to the Fase Address, the phrase 'address on page (page number or name)' will be used to specify an eight bit address within a page. For example, address 01E43A can be identified as address 3A on page 01E4XX.

The term "Base Page" will be used to refer to the lowest order page within a process. This is the 256-byte block of memory whose page address is contained in the Process Base resister. Similarly, the term "Limit Page" will be used to refer to the 256-byte block of memory whose page address is contained in the Process Limit resister. The range of addresses which are available to a process extends from address 00 on the Base Page through address FF on the Limit Page.

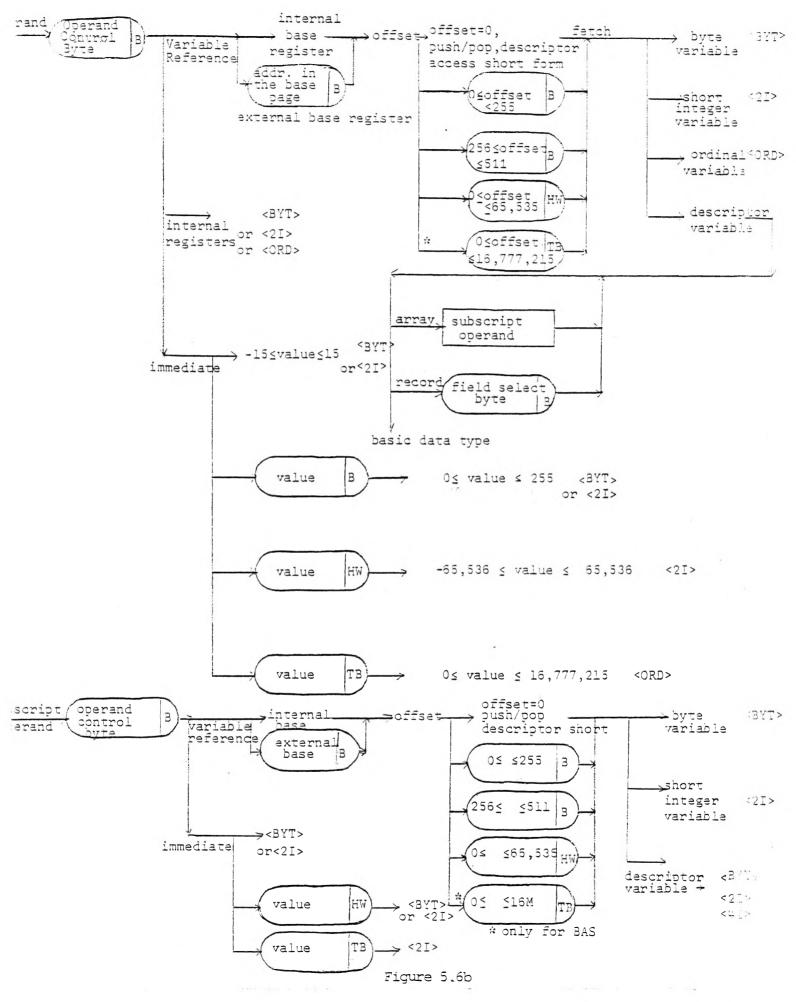

1.3.12 Offset Address, Relative Address

All data addressing within the MCS65E4 is accomplished by adding a displacement to a memory address. This can be divided into two specific forms of addressing. These are Offset Addressing and Relative Addressing. These two differ primarily in the manner in which the memory address and the displacement are specified.

\*\*\*\*\*\*\*CONFIDENTIAL, MOS TECHNOLOGY, INC.\*\*\*\*\*\*\*\* Pase- 17

Within the MCS65E4 architecture, the term 'Offset Addressing' will be used to identify an addressing operation in which the offset is specified in the instruction and the memory address is contained in a base register. Only positive offsets are permitted when accessing through Offset Addressing. The base register can be either one of the on-chip process registers (TOS, BAS, PRM, LMT) or any three-byte set of addresses in the Base Page.

To assure accuracy, this document will utilize the phrase "offset from register (register name)" whenever an Offset Address is specified. In addition, whenever an external base register is established in the process Base Page, this base register will be identified as "EXT (n)", where n is the page address of the start of the base register. For example, if addresses 15-17 on the process Base Fage are to be treated as an external base register, this base will be identified as EXT15. Finally, it will be assumed that a memory location which cannot be accessed through a base resister has no offset address relative to that resister. This will be true, of course, for any memory location outside of the process. Even more important, it will also be true for all memory locations with a lower physical address than that contained in the register since negative offsets are not permitted while accessing data via base registers.

In addition to Offset Addressing, the MCS65E4 utilizes a similar addressing mode in which the memory address is not contained in a base register and in which both negative and positive displacements are permitted. This is termed "Relative Addressing". Within Relative Addressing operations the memory address can be either the contents of the program counter or the address of a data descriptor. This is described in detail in Section 4 of this specification.

| Physical<br>Address                          | Kernel<br>Address    | Operating<br>System<br>Process<br>Address | User<br>Process<br>Address                                                                                                 | Registe                                                  | ers                |

|----------------------------------------------|----------------------|-------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|--------------------|

| Space                                        | Space                | Space                                     | Space                                                                                                                      | Contents                                                 | Name               |

| FFFFF<br> <br> <br> <br> <br>                | FFFFF<br>I<br>I<br>I | OEOOFF                                    | Υ.                                                                                                                         |                                                          |                    |

|                                              |                      |                                           | 0301FF<br> <br> <br> <br>                                                                                                  | 0301XX                                                   | LMT                |

| <br> <br> <br>028000<br> <br> <br> <br> <br> |                      |                                           |                                                                                                                            | · <b></b>                                                |                    |

|                                              |                      |                                           |                                                                                                                            | 024700<br>0235A0<br>023590                               | EXT*<br>TOS<br>PRM |

|                                              |                      |                                           | <br> <br>023500                                                                                                            |                                                          | EXT*<br>Bas        |

| <br> <br> <br> <br> <br>000000               |                      | <br> <br> <br>010000                      | *Base Page Addres<br>assumed to contai<br>set of memory loc<br>treated as an ext<br>register pointing<br>address 024700 (B | n 001200. Th<br>ations will<br>ernal base<br>to physical | is<br>be           |

FIGURE 1.1- Initial Configuration for Addressing Example

\*\*\*\*\*\*\*CONFIDENTIAL, MOS TECHNOLOGY,INC.\*\*\*\*\*\*\*\* Pase- 19

1.4 Example of Addressing within the MCS65E4 System

The addressing concerts outlined above can be clarified by example. This will be accomplished by describing the addresses associated with a memory location which is contained within the address space of a User process. This User process is assumed to have been called by an Operating System process and is therefore at level three in the hierarchy. Any memory location located in this User process can be accessed by each of the lower level processes. Therefore, the memory location being discussed below will have a single physical address, but will have a logical address within the Kernel process, within the Operating System process and within the User process. In addition to these three logical addresses, the memory location will have a number of Offset Addresses during any period that the MCS65E4 is executing one of these three processes.

The diagram above illustrates the memory map of a multi-task system in which the three processes reside. The Kernel is assumed to cover the entire 16-megabyte space. The Operating System process (which was invoked by the Kernel) is limited to the range of addresses from 010000 to 0E00FF. At the same time, the User process is assumed to reside initially within addresses 023500 to 0301FF. The memory location which will be examined initially will be 028000, which is within the range of addresses allocated to the User process. Figure 1.1 illustrates this configuration.

As described previously, each memory location has a single physical address. For the memory location being examined initially, this physical address is 028000. In fact, since the base of the Kernel is always at address 000000, a memory location's logical address within the Kernel is the same as its physical address. Within the Operating System process (level two in the hierarchy) the logical address of this memory location is 018000, which is the displacement between the physical address of the base of the Operating System process and the physical address of the base of the Operating System process and the physical address of the memory location itself. At the same time, this memory location has a logical address within the User process. This is obtained by subtracting the physical address of the memory location (028000) from the physical address of the process base (023500). The resulting logical address is 004B00.

To allow the offset addresses for this memory location to be specified, it is necessary to first specify the contents of the redisters which can be used as a base for addressing the memory location. This will be illustrated by assuming the existence of two addressing redisters, termed the Frimary Base Redister and the Top of Stack Redister. At the same time, it will be useful to assume that addresses 10-12 within the Base Fase contains 001200 and will be treated as an External Base Redister. This provides three internal redisters (including the Frocess Base redister) and one external base redister which can be used to access data.

To illustrate the offset address, assume that the MCS65E4 is executing the User process, the Frimary Base register (FRM) contains 023590 and that the External Base Register (logical

\*\*\*\*\*\*\*CONFIDENTIAL, MOS TECHNOLOGY, INC. \*\*\*\*\*\*\*\* Page- 20

addresses 10-12 within the user process) contains 001200. The Top of Stack Register (TOS) is initially at 0235A0. Under these conditions, the Offset Address of memory location 028000 relative to PRM is 004A70. Likewise, the Offset Address to TOS is 004A60 and the Offset Address to the External Base is 003900.

During the execution of the User process software, it is possible to modify the contents of the addressing resisters introduced above. Doing so, of course, modifies the Offset Address of each memory location in the process relative to that register. It may in fact eliminate the Offset Address since only positive offsets are valid. This can be illustrated by assuming that PRM is set at logical address 000040 within the User process. Doing so sets the register contents to 023540. At this point, the Offset Address of memory location 028000 becomes 004ACO. However, if the PRM is set so that it points to address 029000 (logical address 0005B00 within the User process), this register can no longer be used to access address 028000 and therefore, this memory location no longer has an offset to the PRM register.

It should be noted that all memory locations outside the limits of a process have no logical addresses within that process. Likewise, memory locations outside of a process which is being executed have no Offset Address relative to the internal or external base registers since these locations cannot be accessed by these registers.

2.0 Description of the MCS65E4 Fin Functions

2.1 Introduction

The initial versions of the MCS65E4 will be available in a standard 40-pin dual-in-line package. This is made possible by multiplexing the address, data and bus status information onto a set of 24 pins. The pin configuration is as follows:

| Function |                                                       | t of pins |

|----------|-------------------------------------------------------|-----------|

| 1.       | Address Bus Middle/ Address Bus Low<br>(A9/A1-A16/A8) |           |

| $\gamma$ | Address Bus High/ Data Bus Lo                         | 8         |

| • خد     | (A16/DB0-A23/DB7)                                     | 8         |

| 3.       | Bus Status/ Data Bus High                             | 0         |

| •••      | (IACK/DB8-MIC/DB15)                                   | 8         |

| 4.       | Row Address Strobe (RAS)                              | 1         |

|          | Column Address Strobe (CAS)                           | 1         |

| 6.       | Chip power (VDD,VSS)                                  | 2         |

| 7.       | Oscillator                                            | 2         |

| 8.       | Bus Clock (BCLK)                                      | 1         |

| 10.      | Memory Ready (RDY)                                    | 1         |

| 11.      | Interrupt Input (INT)                                 | 1         |

| 12.      | Reset (RES)                                           | 1.        |

| 13.      | Write Enables (WEL, WEH)                              | 2         |

| 14.      | Bus Error (BERR)                                      | 1         |

| 15.      | Hold (HLD)                                            | 1         |

| 13.      | Instruction Intercept (II)                            | 1         |

|          |                                                       |           |

TOTAL 40

Each of these sets of pins is described in detail below.

2.2 Address Bus Middle/Address Bus Low (A9/A1-A16/A8)

The low order sixteen address bits (above AO) are multiplexed onto eight pins in a manner which is compatible with industry standard 64-Kbit dynamic RAMS. These lines enter the high impedance state for external IMA operations (see HOLD).

2.3 Address Bus/Data Bus/Bus Status (A16/DB0-A23/DB7, IACK/DB8-MIC/DB15)

The high order eight address bits and the bus status bits are multiplexed with the bi-directional data bits. During memory write operations, the timing for these signals is the same as for the low order sixteen address lines. For a memory read operation, the MCS65E4 output drivers enter the high impedance state and the memory devices place data onto these lines.

The high order address bits are normally stored in external latches to be used as chip selects for the memory and I/O devices. These signals are strobed by RAS as are the bus status bits. The bus status bits are used to control specific functions such as interrupt and DMA.

\*\*\*\*\*\*CONFIDENTIAL, MOS TECHNOLOGY,INC.\*\*\*\*\*\*\*\* Page- 22

Status Function Bit ---------S1 Interrupt Acknowledge (IACK) S2 Hold Acknowledge (HOLDA) S3 Last Instruction Cycle (LIC) S4 I/O Reset (IORES) Processor Instruction Fetch (INST) S5 Processor Data Fetch (DAT) S3 S7 Refresh Cycle (REF) S8 External Microcode Fetch (MIC)

2.3.1 Interrupt Acknowledge (IACK)

The IACK bit soes high to signal the Interrupt Controller that it can place the active interrupt request information on the low order eight bits of the data bus. This operation is described in detail in Section 4,4,4,13.

2.3.2 Hold Acknowledge (HOLDA)

The Hold Acknowledge bit goes high to indicate that the processor will enter the HOLD state at the end of the present cycle. During the HOLD state, the RAS and CAS signals continue to run and the bus status signals are generated by the processor during RAS. However, no data, address or write enable (WEL, WEH) information is generated and the corresponding drivers remain in the high impedance state at the appropriate time.

2.3.3 Last Instruction Cycle (LIC)

The LIC bit does high to indicate that the current cycle is the last cycle of an instruction execution sequence. This is used in conjunction with bus arbitration logic in multi-processor systems to control access to shared resources.

2.3.4 I/O Reset (IORES)

This bit does low to cause the system I/O devices to be reset. This occurs when a System Reset instruction is executed. Causing the RES input signal to do low does not cause this bus status bit to do low. This allows resetting the processor without effecting the peripheral devices.

2.3.5 Processor Instruction Fetch

This bit does high to indicate that the address on the address bus comes from the Processor Program Counter and that the data being fetched from memory will be placed into the input queue,

2.3.6 Processor Data Fetch

This bit does high to indicate that the address on the address bus was denerated as the result of an instruction execution,

2.3.7 Refresh Cycle

\*\*\*\*\*\*\*CONFIDENTIAL, MOS TECHNOLOGY, INC. \*\*\*\*\*\*\*\* Pase- 23

This bit does high to indicate that the current cycle is a memory refresh cycle.

2.3.8 External Microcode Fetch

This bit goes high to indicate that the current cycle is an external microcode fetch cycle.

2.4 Row Address Strobe (RAS)

The Row Address Strobe is a clock signal used primarily to latch the middle eight bits of the address into external latches. These can be discrete TTL latches for interfacing to peripheral devices or to conventional static memories. In most cases, however, they will be located in the dynamic memory devices. In addition to the middle byte of the address bus, this signal indicates the presence of valid data on the high order address lines and on the Bus Status lines. RAS will be held low by RDY but will continue running during a HOLD operation.

2.5 Column Address Strobe (CAS)

The Column Address Strobe is primarily used to latch the column addresses (low order eight address bits) into external latches. This signal is also used to indicate that valid data is present on the data lines during a memory write operation and to enable the memory output drivers during a memory read operation. This signal is synchronous with the BCLK signal. The CAS signal is held low by RDY but will continue running during a HOLD operation.

2.6 Chip Power (VDD,VSS)

The MCS65E4 will by powered by  $\pm 5.0$  Volts DC applied between the VDD and VSS pins (VDD =  $\pm 5.000$  VSS = Ground).

2.7 Oscillator (Osc In, Osc Out)

The 8 Mhz oscillator can be controlled by a quartz crystal connected between the Oscillator In and Oscillator Out pins. In addition, the chip can be controlled by an external oscillator by driving the Oscillator In pin with a TTL level square wave.

2.8 Bus Clock (BCLK)

The Bus Clock corresponds to the normal Phase Two clock in the 6502 microprocessor system. Since this signal is always present, it can be used to synchronize the RDY, HOLD and BERR signals and to control data transfers between the MCS65E4 and any 6502 interface device.

2.9 Valid Memory Address

This bit goes high to indicate that there is a valid memory address on the address bus,

\*\*\*\*\*\*\*CONFIDENTIAL, MOS TECHNOLOGY, INC.\*\*\*\*\*\*\*\* Pase- 24

2.10 Memory Ready (RDY)

The Memory Ready input can be used to control the operation of the processor when interfacing to slower memory or peripheral devices. This signal operates in the same manner as in the 6502 microprocessor system with the additional capability of being able to stop on both a read and a write operation. These two operations are described separately below. The dynamic memory refresh operation is disabled as long as RDY is held low.

2.10.1 Operation of RDY during Read Cycle

At the beginning of a memory read operation, the processor places A9-A23 and the bus status information on the multiplexed address/data lines. This is followed by RAS going low to cause this information to be latched externally. The address and bus status information is then changed to A1-A8 and D0-D15. This is followed by CAS going low and BCLK going high.

Immediately after BCLK does high, the RDY line can be pulled low to cause the processor to stop in its current state. If RDY is pulled low during a memory read operation, the processor stops with the data bus lines in the high impedance state. The RAS and CAS signals remain low as long as RDY remains low. This will hold the address in the external latches allowing whatever time is necessary for the memory outputs to become valid.

2.10.2 Operation of RDY during Write Cycle

Timins for the Write cycle is very similar to that described above for the Read cycle. The Write Enable Signals (WEL, WEH) will go low immediately after the beginning of the cycle (coincident with A9-A16 going valid). Immediately after RAS goes low, the data to be written into memory is placed on the DBO-DB15 lines. If RDY is pulled low during this cycle, the RAS and CAS signals remain low and the processor output data will remain on the DBO-DB15 lines. The Write Enable lines will go high coincident with the trailing edge of the BCLK pulse during which the RDY line returns high.

2.11 Interrupt Input (INT)

The MCS65E4 processor can be interrupted through the Interrupt Input. Setting the INT pin low causes the MCS65E4 to enter an interrupt sequence at the end of the current instruction if the Interrupt Inhibit bit in the Process Control Register is cleared. The operation of the interrupt function is described in detail in Section 4.0.

2,12 Reset (RES)

The processor can be reset by applying a low signal to this input. For power-on reset, this can be accomplished by connecting an R-C circuit to the RES pin. Positive control of the reset function in the peripheral devices can be accomplished by connecting these devices to the IORES Bus Status bit. As long as the reset input stays low, the processor will not perform any write operations.

\*\*\*\*\*\*\*CONFIDENTIAL, MOS TECHNOLOGY,INC.\*\*\*\*\*\*\*\*\* Page- 25

-----

# 2.13 Write Enables (WEL,WEH)

The write-enable signals control the direction of data transfers between the MCS65E4 and memory. If a write-enable line is high (Read), data will be transferred from memory to the processor. If this signal is low, data will be transferred into memory. WEL controls writing into the lower byte im memory (even addresses) while WEH controls writing into the the upper byte (odd addresses).

2.14 Bus Error

The Bus Error pin can be used to indicate that an error occurred during the previous cycle. This error can be the result of a Virtual Memory Address fault, a data error detected in an external EDC chip, or any other form of error. When this occurs, the processor immediately suspends its current execution sequence and traps to the operating system. The operating system can process the error and, if appropriate, can then return to the execution sequence which was interrupted.

2.15 Hold (HOLD)

The Hold pin can be pulled low to cause the processor to stop and to place its address and data bus into the high impedance state. This is used primarily for external DMA and multiprocessor operations. As long as the HOLD pin is low, the RAS and CAS signals continue to operate normally and the processor continues to put out the Bus Status bits. However, no address or data signals are generated by the processor and the corresponding pins remain in the high-impedance state except as required to generate the bus status information and to perform the required refresh operations. If the external memory refresh is enabled during the hold state (Hold = Low), the HOLDA bus status bit will return low periodically to signal the external devices that the processor will place refresh addresses on the address bus

2.16 Instruction Intercept (II)

The Instruction Intercept can be used to cancel the execution of an instruction within the MCS65E4. If this line is pulled low, the current instruction execution terminates immediately. The processor then treats the next byte in program sequence as an Op Code and immediately enters the appropriate execution sequence. This pin is used primarily by Auxiliary Arithmetic Processors to cancel the execution of intercepted instructions.

3.0 Internal architecture of the MCS65E4

3.1 Introduction

All aspects of the internal MCS65E4 architecture are designed to achieve the desired level of performance in the smallest possible chip size. Most of the registers are organized into a single dynamic array with all data modification taking place in a high-speed 8-bit ALU. Four internal cycles are executed for each external (processor) cycle. This ratio of internal to external cycles combined with the fact that the ALU is utilized in nearly every internal cycle allows full 2 MHz operation in a processor containing a full 64 bytes of register within a chip size usually associated with 8 bit processors.

It should be noted that the device described below is only the first implementation of the architecture described in this document. This implementation tries to achieve a balance between chip size and capability with a strong emphasis on minimizing chip cost. It is assumed that future implementations of this architectute will result in devices with increased capability through larger control ROMS, through the integration of additional system functions (keyboard interface, etc.) onto the processor, and ultimately, by expanding the internal organization from 8 to 32 bits. All of these configurations will be upward compatible with the earlier devices.

The MCS65E4 is organized into an Execution Unit and an Execution Control Unit. Each of the major components which comprise these two units is described briefly below.

3.2 Execution Unit

3.2.1 ABL/ABM Registers

Those registers which are associated with the multiplexed low order sixteen address pins are located in a single dynamic array. These registers are:

Program Counter Low and Middle

Refresh Register

Address Register 1 Low and Middle

Address Register 2 Low and Middle

Address Register 3 Low and Middle

These registers are supported by an eight-bit incrementer which operates in parallel with the ALU described below.

3.2.2 Resister Array

The complete register array is contained in a matrix of dynamic RAM cells. The traditional 3-2-2 dynamic RAM cell has been expanded to allow two READ buses and one WRITE bus. The register refresh operation is handled by a combination of hardware and software in a manner which is totally transparent to the user.

\*\*\*\*\*\*\*CONFIDENTIAL, MOS TECHNOLOGY,INC.\*\*\*\*\*\*\*\* Page- 27

3.2.3 Arithmetic/Logic Unit (ALU)

Most of the data modification operations take place in the ALU. This includes normal execution operations as well as middle and high order Program Counter incrementing and register incrementing, decrementing, etc. The ALU is equipped with high speed carry look-ahead to allow it to complete any operation within one internal cycle. This allows an 8-bit ALU to perform most of the data manipulation functions required by a 32-bit processor.

The specific functions performed in the ALU are as follows:

- 1. Data shifting

- 2. Address limit checking

- 3. 2's complement binary addition and subtraction

- 4. Packed BCD addition and subtraction

- 5. Losic AND

- 6. Losic OR

- 7. Losic EOR

## 3.2.4 Input Queue

Data which is fetched from memory under control of the program counter is first loaded into the input queue where it is held until it is needed by the control logic. The queue is usually filled by "pre-fetching" the next instruction sequence during each execution.

3.2.5 ABH/DB Registers

All of the registers associated with the Data Bus and the Address Bus High are located in a single dynamic array. This facilitates the multiplexing of these signals onto a set of sixteen pins as described in Section 2. These registers are as follows:

Program Counter High

Data Latch Low and High

Address Register 1 High

Address Register 2 High

Address Register 3 high

The bus status signals are generated in the control section and are multiplexed with the appropriate data bus signals at the bonding pad.

3.3 Execution Control Losic

3.3.1 Control Registers

All of the registers needed to assure proper instruction execution are contained in the Control Register Section. These registers perform such operations as storing execution control flags, selecting registers within the register array, counting execution cycles and addressing the microcode array.

3.3.2 Microcode Array

-----

\*\*\*\*\*\*\*CONFIDENTIAL, MOS TECHNOLOGY,INC.\*\*\*\*\*\*\*\*\* Page- 28

-----

· · · · · · ·

Both the microcode ROM and the Nanocode ROM are located in a single array. This assures minimum chip size since only one set of buses, decoder/drivers, etc. is required. In addition, this array is organized in a manner which allows the total size of the ROM to be varied without affecting the remainder of the chip. This will allow the rapid generation of additional versions of the processor which provide additional capability through expanded microcode.

\*\*\*\*\*\*\*CONFIDENTIAL, MOS TECHNOLOGY,INC.\*\*\*\*\*\*\*\* Pase- 29

4.0 MCS65E4 Microprocessor Software Architecture

4.1 Introduction

The primary goal of the MCS65E4 architecture is to shorten the gap between the processor hardware and the high level language architecture while at the same time retaining the generality which will allow it to support a broad range of applications. In particular, the software architecture of the MCS65E4 exhibits the following characterictics:

- 1. Strong multi-tasking support.

- 2. Separation between data and program.

- 3. "Three-operand" addressing, i. e., all data operations are memory-to-memory.

- 4. Data structures (array, record, etc.) directly resembling high-level language practices.

4.2 MCS65E4 Internal Architecture

4.2.1 Introduction

The internal architecture of the MCS65E4 contains all of the registers needed to support execution of the instruction set described in Section 4.8. This set of registers is divided into those which are visible to the programmer (hereafter referred to as the Process Registers) and a set of temporary data registers which are used during instruction execution. The process registers are as follows:

- 1. Process Base Register (BAS)

- 2. Process Limit Register (LMT)

- 3. Process Program Counter (PPC)

- 4. Primary Base Register (PRM)

- 5. Top of Stack Redister (TOS)

- 6. Process Control Register (PCR)

It should be noted that for speed purposes, the internal process registers (PRM, TOS, LMT, and PPC) contain physical addresses during process execution. However, the MCS65E4 user does not see these physical addresses since they are converted to logical addresses whenever the contents of one of these registers is transferred into memory. This is accomplished by subtracting the contents of the Process Base Register (BAS) from the address being transferred into memory. Similarly, the logical addresses contained in memory are converted to physical addresses when the internal process registers are loaded.

4.2.2 Process Base Resister (BAS)

The Process Base Register sets the lower limit of the memory space in which the process must execute. This memory space starts at the first byte of the page whose address is contained in BAS, i.e., the BAS register contains the page number of the physical address at which the process starts. For example, if the BAS register contains 04E7, the lowest address which is available to the

\*\*\*\*\*\*\*CONFIDENTIAL, MOS TECHNOLOGY,INC.\*\*\*\*\*\*\*\* Page- 30

process is 04E700.

4.2.3 Process Limit Register (LMT)

The Process Limit Redister sets the upper limit of the memory space in which a process is to execute. At the same time, it identifies a page in memory which is used to store exception vectors and other information required to control execution of the process. The highest address available to a process is the last byte of the Limit Page. For example, if the LMT redister contains OD34, the highest available address in the process is OD34FF.

4.2.4 Process Program Counter (FPC)

Execution of MCS65E4 programs proceeds under control of the Process Program Counter. The operations associated with this register are much the same as in any programmable processor.

4.2.5 Primary Base Register (PRM)

The Primary Base redister is provided to control the accessing of data during instruction execution. Address offsets contained in the MCS65E4 instructions are added to the PRM redister to obtain the physical address of the data.

4.2.6 Top of Stack Resister (TOS)

The Top of Stack Resister controls access to the process stack during instruction execution. The stack and Top of Stack Resister (TOS) operate in a conventional manner to store subroutine return addresses, subroutine data, interrupt return addresses, etc. In addition, the TOS can be used as a base resister to control the accessing of data in memory utilizing offset addressing. This operates in exactly the same manner as does Offset Addressing using the Frimary Base (FRM) resister.

4.2.7 Process Control Register (PCR)

The Process Control Register contains a number of flags and control bits which are used to control instruction execution within the processor. The PCR register bits are:

| Bit | Designation                                                      |

|-----|------------------------------------------------------------------|

| 0   | K - Kernel Mode Fla⊴                                             |

| 1   | U - User/Supervisor Mode                                         |

| 2   | I - Interrupt Inhibit Flag                                       |

| 3   | E - Enable External Memory Refresh                               |

| 4   | P - Enable Periodic Interrupt<br>S - Enable Stack Boundary Check |

| 6   | D - Debus Mode                                                   |

| 7   | T - Disable All Traps                                            |

|     | M - Microcode Select<br>R - Refresh Rate                         |

4.2.7.1 Kernel Mode Flag (K)

The Kernel state (K = 1) represents the first level of the operating system. This flag is set and cleared sutomatically as the processor moves into and out of the Kernel state.

4.2.7.2 User/Supervisor Mode (U)

The User/Supervisor flag is set to a logic 1 to enable execution of a number of privileged instructions which are normally available only to the operating system. This flag is set automatically by the Reset input or when the processor exits from a User process. It is cleared when a User process is invoked.

4.2.7.3 Interrupt Inhibit Flag (I)

The Interrupt Inhibit Flag can be set to disable interrupts on the INT input.

4.2.7.4 Enable External Memory Refresh (E)

The E flag must be set to a logic 1 to enable the processor to perform periodic external memory refresh operations. The internal refresh logic will assure that each row in the dynamic memories will be refreshed at a rate determined by the programmable Refresh Control Counter.

4.2.7.5 Enable Periodic Interrupt (P)

The P flag can be set to a logic 1 to cause the processor to execute a trap each time the memory refresh logic 'rolls over'. This occurs at a rate determined by the Refresh Control Counter (typically between 2 and 4 milliseconds). This trap will occur whether or not the external refresh operation is enabled.

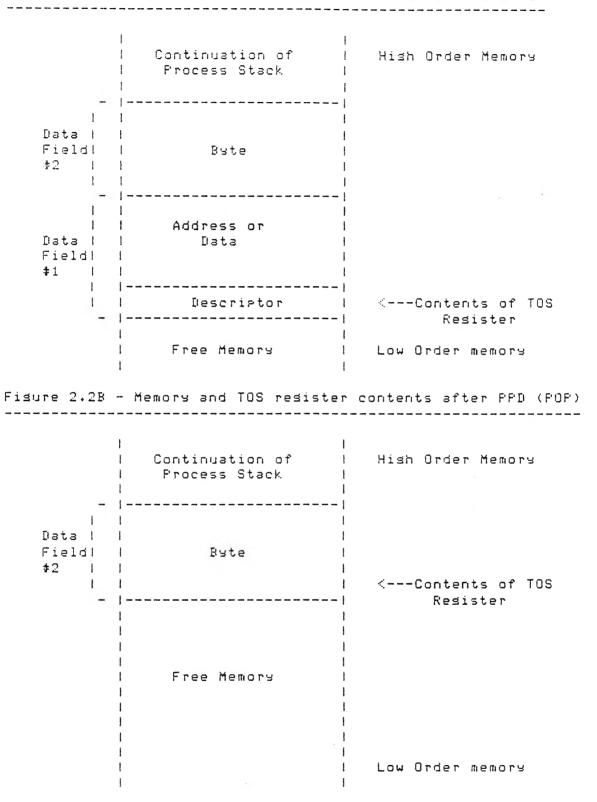

4.2.7.6 Enable Stack Boundary Check (S)

The S flag can be set to cause the processor to execute a trap whenever the stack crosses a page boundary during a PUSH or POP operation. This allows either the process or the operating system to verify that the stack will not over-write data in memory.

4.2.7.4 Debus Mode (D)

The Debus flas can be set to allow single-instruction execution of a User process. Each time the processor enters a User process it will execute a single instruction and will then trap back to the operating system, allowing the operating system to display the effects of each instruction execution for debug purposes.

4.2.7.8 Enable Read Before Byte Write (W)

All traps are disabled if this flag is set.

4.2.7.9 Microcode Select (M)

\*\*\*\*\*\*\*CONFIDENTIAL, MOS TECHNOLOGY, INC.\*\*\*\*\*\*\*\* Pase- 32

These four bits directly reflect the contents of the internal Microcode Select Register. This data is placed onto bits 12-15 of the address bus during an external microcode fetch.

4.2.7.10 Refresh Rate

These four bits directly reflect the contents of the internal Refresh Control Register. This data directly controls the rate at which the MCS65E4 refreshes the external memories.

\*- Kernel and Supervisor Process only

.

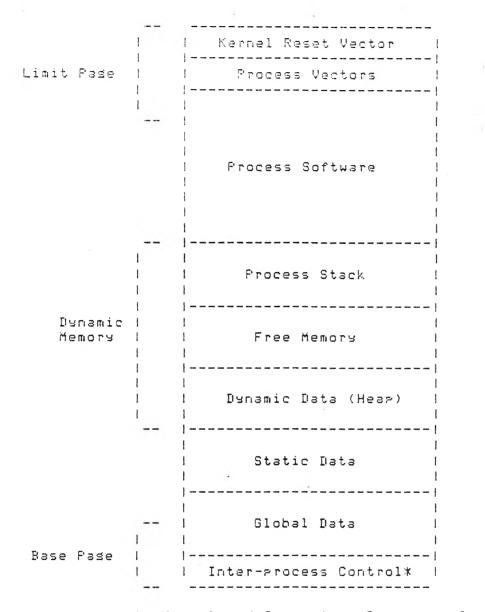

Figure 4.0 Suggested Process Organization in the MCS65E4 System

4.3 Process Structure

4.3.1 Introduction

Those factors which influence the organization of a process within the MCS65E4 are much the same as the factors which govern the organization of memory within an MCS6502 system. These are as follows:

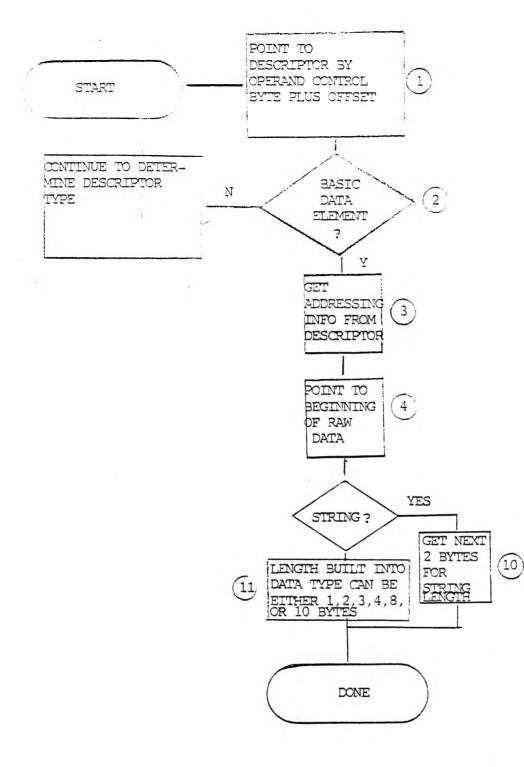

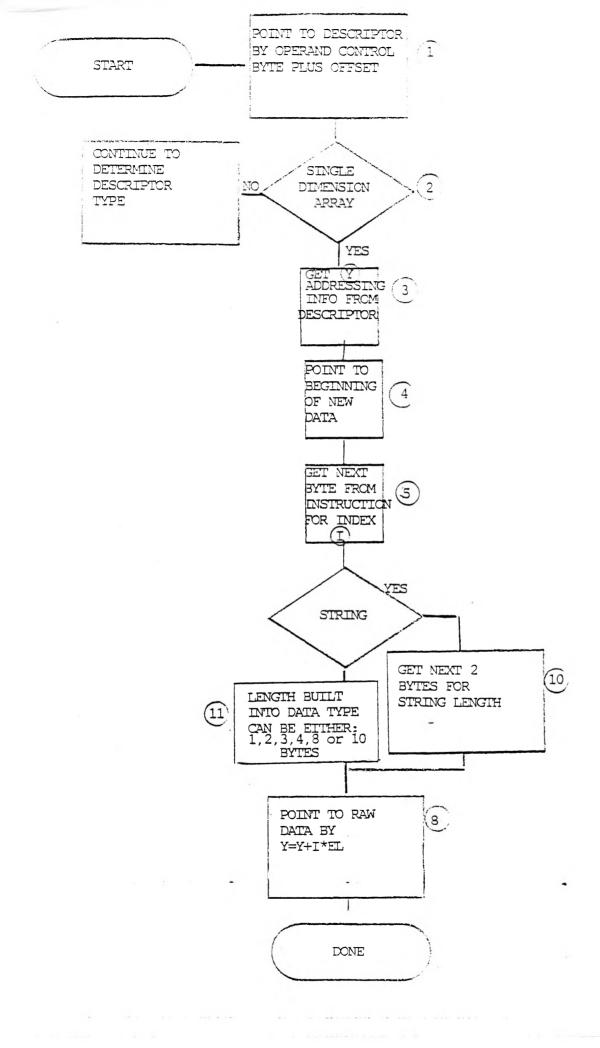

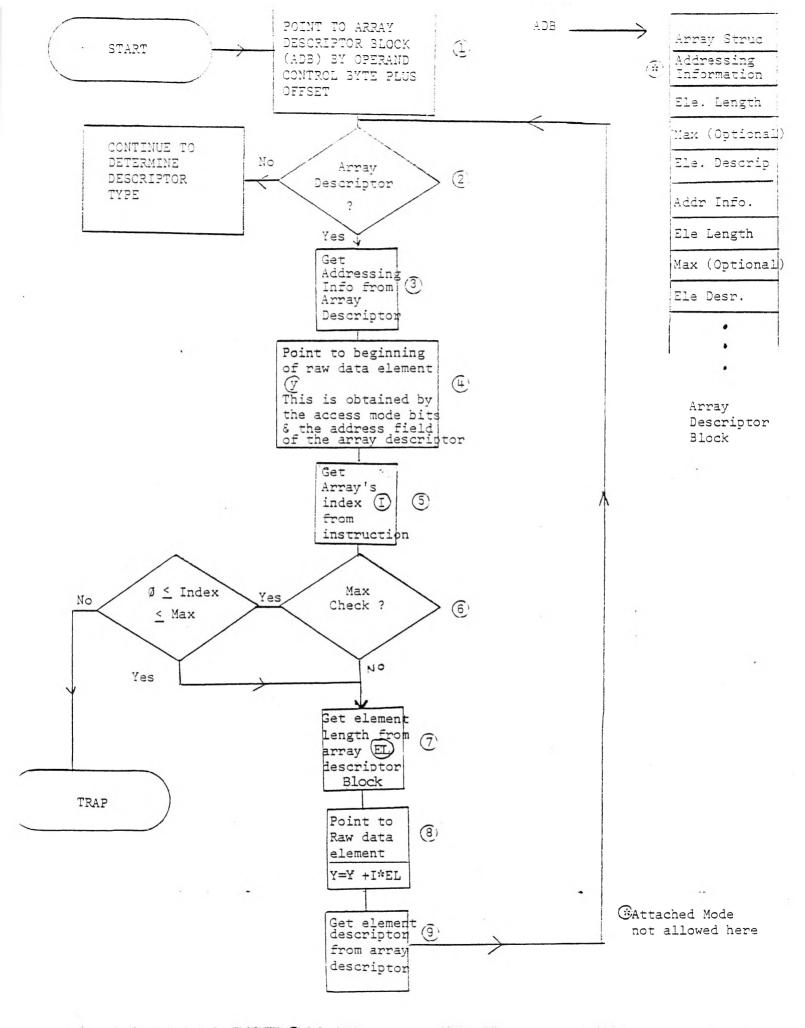

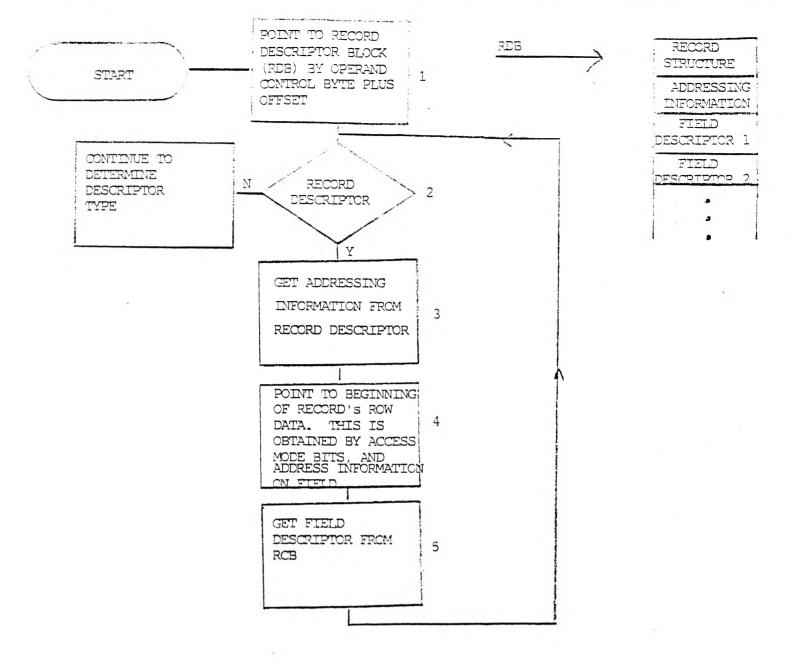

- The vectors associated with the processing of interrupts, system calls, etc. are located in the Limit page, i. e., in high order memory. This generally dictates that program memory be at the upper limit of the address space allocated to the process.