950 Rittenhouse Rd., Norristown, PA 19403 • Tel.: 215/666-7950 • TLX 846-100 MOSTECHGY VAFG

# 6525 TRI-PORT INTERFACE

## CONCEPT ...

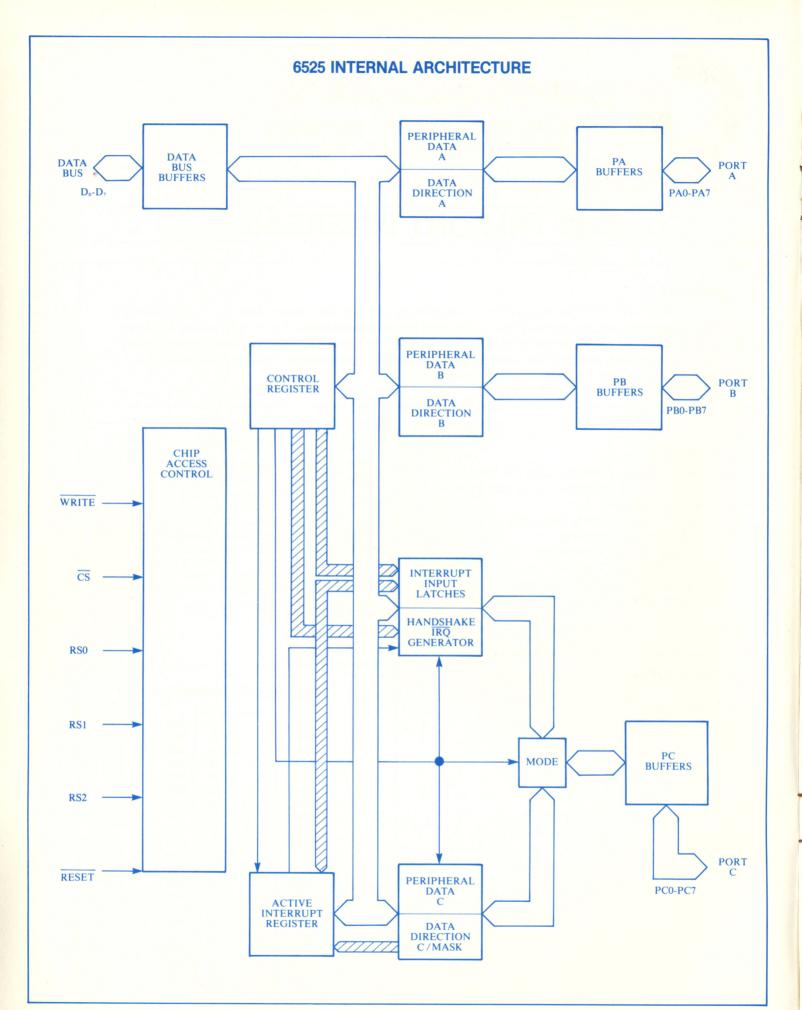

The 6525 TRI-PORT Interface (TPI) is designed to simplify the implementation of complex I/O operations in microcomputer systems. It combines two dedicated 8-bit I/O ports with a third 8-bit port programmable for either normal I/O operation or priority interrupt/handshaking control. Depending on the mode selected, the 6525 can provide 24 individually programmable I/O lines or 16 I/O lines, 2 handshake lines and 5 priority interrupt inputs.

#### **FEATURES:**

- 24 individually programmable I/O lines or 16 I/O lines, 2 handshake lines and 5 interrupt inputs.

- Priority or non-priority interrupts

- Automatic handshaking

- Completely static operation

- Two TTL Drive Capability

- 8 directly addressable registers

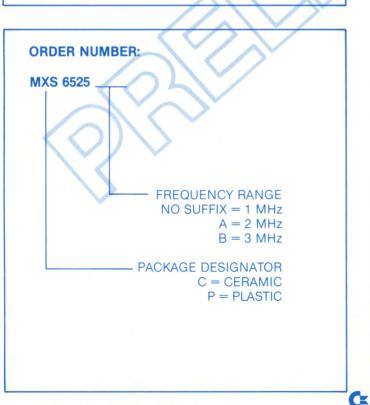

- 1 MHz, 2MHz and 3MHz operation

|      | Statement of the local division of the local |           | obeo maanooomig                  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|----------------------------------|

| 65   | 525 RE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | GISTER    | S/(Direct Addressing)            |

| *00  | 00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | R0        | PRA-Port Register A              |

| 00   | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | R1        | PRB-Port Register B              |

| 01   | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | R2        | PRC-Port Register C              |

| 01   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | R3        | DDRA – Data Direction Register A |

| 10   | 00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | R4        | DDRB-Data Direction Register B   |

| 10   | )1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | R5        | DDRC – Data Direction Register   |

| V    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |           | C/Interrupt Mask Register        |

| > 11 | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | <b>R6</b> | CR-Control Register              |

| 11   | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | R7        | AIR – Active Interrupt Register  |

| *1   | NOTE:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | RS2, RS   | S1, RS0 respectively             |

6525 Addressing

#### **6525 PIN CONFIGURATION** 1 40 DB7 VSS DB6 39 PA0 2 PA1 3 38 DB5 PA2 4 37 DB4 PA3 5 36 DB3 DB2 PA4 6 35 PA5 7 34 DB1 PA6 33 DB0 8 PA7 9 32 PC7 PB0 10 31 PC6 30 PC5 PB1 11 29 PC4 PB<sub>2</sub> 12 PB3 13 28 PC3 PB4 27 PC2 14 PC1 PB5 15 26 PCO PB6 16 25 PB7 17 24 RS0 CS RS1 18 23 WRITE 19 22 RS<sub>2</sub> RST 21 VDD 20

A COMMODORE COMPANY

# **MAXIMUM RATINGS**

| RATING                      | SYMBOL           | VALUE         | UNIT            |

|-----------------------------|------------------|---------------|-----------------|

| SUPPLY VOLTAGE              | V <sub>cc</sub>  | -0.3 to +7.0  | V <sub>dc</sub> |

| INPUT VOLTAGE               | Vin              | -0.3 to +7.0  | V <sub>dc</sub> |

| OPERATING TEMPERATURE RANGE | TA               | 0 to + 70     | °C              |

| STORAGE TEMPERATURE RANGE   | T <sub>stg</sub> | - 55 to + 150 | °C              |

This device contains circuitry to protect the inputs against damage due to high static voltages, however, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum rated voltages to this circuit.

# CHARACTERISTICS (V<sub>CC</sub> = 5.0 V $\pm$ 5%, V<sub>SS</sub> = 0V, T<sub>A</sub> = 0° to 70°C)

| CHARACTERISTIC                                                                                                                                                                                                      | SYMBOL           | MIN   | ТҮР    | MAX   | UNIT |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------|--------|-------|------|

| Input High Voltage (Normal Operating Levels)                                                                                                                                                                        | VIH              | + 2.0 | -      | Vcc   | Vdc  |

| Input Low Voltage (Normal Operating Levels)                                                                                                                                                                         | VIL              | - 0.3 | -      | + .8  | Vdc  |

| Input Leakage Current<br>V <sub>in</sub> = 0 to 5.0 Vdc<br>WRITE RST, CS, RS <sub>0</sub> -RS <sub>2</sub>                                                                                                          | IIN              | _     | ± 1.0  | ± 2.5 | μAdc |

| Three-State (Off State Input Current)<br>(V <sub>in</sub> = 0.4 to 2.4 Vdc, V <sub>CC</sub> = max)<br>DØ-D7                                                                                                         | ITSI             | _     | ± 2.0  | ± 10  | μAdc |

| Output High Voltage<br>(V <sub>CC</sub> = min, Load = 200 μAdc)                                                                                                                                                     | ∨он              | 2.4   | _      | _     | Vdc  |

| Output Low Voltage<br>(V <sub>CC</sub> = min, Load = 3.2 mAdc)                                                                                                                                                      | VOL              | _     | _      | + 0.4 | Vdc  |

| Output High Current (Sourcing)<br>(V <sub>OH</sub> = 2.4 Vdc)                                                                                                                                                       | юн               | -200  | - 1000 | _     | μAdc |

| Output Low Current (Sinking)<br>(V <sub>OL</sub> = 0.4 Vdc)                                                                                                                                                         | IOL              | 3.2   | -      | _     | mAdc |

| Supply Current                                                                                                                                                                                                      | Icc              | —     | 50     | 100   | mA   |

| Input Capacitance<br>$(V_{in} - O, T_A = 25^{\circ}C, f = 1.0 \text{ MHz})$<br>$D \oslash \text{-}D7, PA \oslash \text{-}PA7, PB \oslash \text{-}PB7, PCO-PC7,$<br>WRITE RST, RS <sub>0</sub> -RS <sub>2</sub> , CS | C <sub>in</sub>  | _     | -      | 10    | pF   |

| Output Capacitance<br>(V <sub>in</sub> - 0, T <sub>A</sub> = 25°C, f = 1.0 MHz)                                                                                                                                     | C <sub>out</sub> | _     | _      | 10    | pF   |

Note: Negative sign indicates outward current flow, positive indicates inward flow.

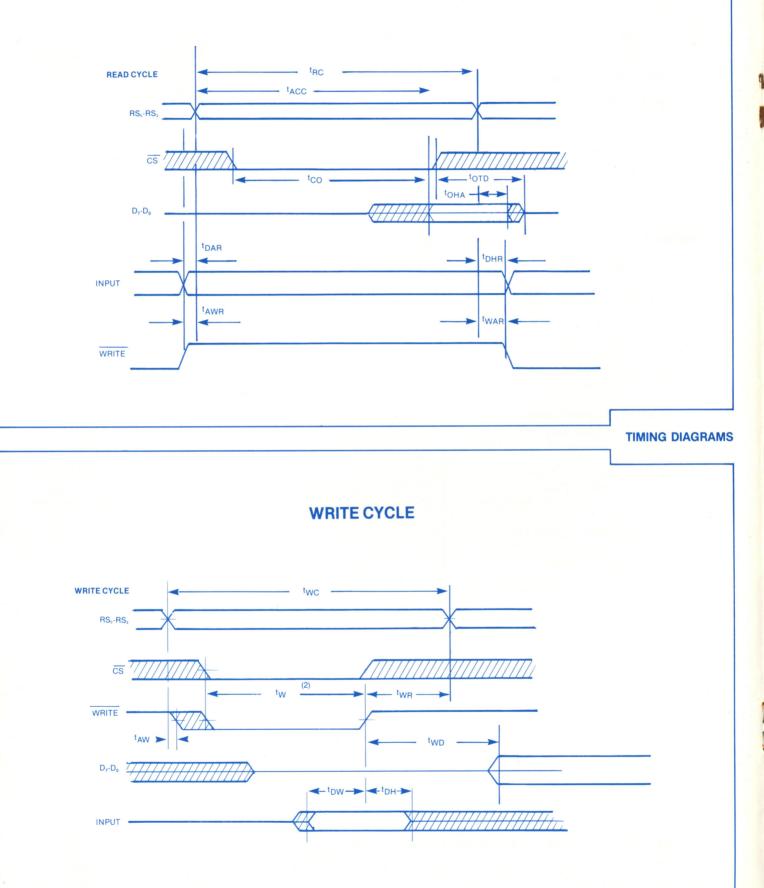

**READ CYCLE**

4

# **READ CYCLE**

|                  |                                    | 11  | MHz       | 2   | MHz | 31  | MHz |       |

|------------------|------------------------------------|-----|-----------|-----|-----|-----|-----|-------|

| Symbol           | Parameter                          | MIN | MAX       | MIN | MAX | MIN | MAX | UNITS |

| tRC              | Read Cycle Time                    | 700 |           | 350 |     | 220 |     | nS    |

| tACC             | Access time                        | 450 |           | 200 |     | 130 |     | nS    |

| tco              | Chip Select to Output Valid        | 450 |           | 200 |     | 130 |     | nS    |

| tOTD             | Chip Deselected to Output Off      | 0   | 100       | 0   | 100 | 0   | 100 | nS    |

| <sup>t</sup> OHA | Output Hold From<br>Address Change | 50  |           | 50  |     | 50  |     | nS    |

| tDAR             | Peripheral Data Set-Up             | 90  |           | 80  |     | 60  |     | nS    |

| <sup>t</sup> DHR | Peripheral Data Hold               | 0   | 1008-1341 | 0   |     | 0   |     | nS    |

| tAWR             | Write to Address Setup             | 0   |           | 0   |     | 0   |     | nS    |

| tWAR             | Write to Address Hold              | 0   |           | 0   |     | 0   |     | nS    |

# WRITE CYCLE

|                 |                              | 11   | /IHz | 2   | MHz | 31  | 1Hz |       |

|-----------------|------------------------------|------|------|-----|-----|-----|-----|-------|

| Symbol          | Parameter                    | MIN  | MAX  | MIN | MAX | MIN | MAX | UNITS |

| tWC             | Write Cycle Time             | 700  |      | 350 |     | 220 |     | nS    |

| tAW             | Address to write set-up time | 0    |      | 0   |     | 0   |     | nS    |

| tw              | Write Pulse Width            | 450  |      | 200 |     | 130 |     | nS    |

| tWR             | Write Release Time           | 250  |      | 150 |     | 90  |     | nS    |

| tDW             | Data to Write Overlap        | 150  |      | 75  | 1   | 75  |     | nS    |

| <sup>t</sup> DH | Data Hold                    | 50   |      | 50  |     | 50  |     | nS    |

| tWD             | Write to Peripheral Output   | 1000 |      | 500 |     | 330 |     | nS    |

|                 |                              |      |      |     |     |     |     |       |

MOS TECHNOLOGY, INC. reserves the right to make changes to any products herein to improve reliability, function or design. MOS TECHNOLOGY, INC. does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights nor the rights of others.

5

| 6525 Control Reg    | gisters |                 |                 |                 |                |                 |                |                |  |

|---------------------|---------|-----------------|-----------------|-----------------|----------------|-----------------|----------------|----------------|--|

| CR                  | CB1     | CB <sub>0</sub> | CA <sub>1</sub> | CA <sub>0</sub> | IE4            | IE <sub>3</sub> | IP             | MC             |  |

| AIR                 |         |                 |                 | A <sub>4</sub>  | A <sub>3</sub> | A <sub>2</sub>  | A <sub>1</sub> | A <sub>0</sub> |  |

| DDRC<br>When MC = 1 |         |                 |                 | M <sub>4</sub>  | M <sub>3</sub> | M <sub>2</sub>  | M <sub>1</sub> | M <sub>0</sub> |  |

| PRC<br>When MC = 1  | СВ      | CA              | ĪRQ             | I <sub>4</sub>  | l <sub>3</sub> | l <sub>2</sub>  | l <sub>1</sub> | lo             |  |

# CA, CB Functional Description

The CA, CB lines are outputs used in the same fashion as the  $CA_2$  and  $CB_2$  output of the 6520.

| CA OUTPUT MOI | DES |

|---------------|-----|

|---------------|-----|

| CA <sub>1</sub><br>0 | CA <sub>0</sub><br>0 | MODE<br>"Handshake"<br>on Read | DESCRIPTION<br>CA is set high on an active transition of the I <sub>3</sub> interrupt input signal<br>and set low by a microprocessor "Read A Data" operation. This<br>allows positive control of data transfers from the peripheral device to<br>the microprocessor. |

|----------------------|----------------------|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0                    | 1                    | Pulse Output                   | CA goes low for IMS after a "Read A Data" operation. This pulse can be used to signal the peripheral device that data was taken.                                                                                                                                      |

| 1                    | 0                    | Manual<br>Output               | CA set low.                                                                                                                                                                                                                                                           |

| 1                    | 1                    | Manual<br>Output               | CA set high.                                                                                                                                                                                                                                                          |

# **CB OUTPUT MODES**

| CB <sub>1</sub> | CB <sub>0</sub> | MODE                    | DESCRIPTION                                                                                                                                                                                                                                              |

|-----------------|-----------------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0               | 0               | "Handshake"<br>on Write | CB is set low on microprocessor "Write B Data" operation and is set<br>high by an active transition of the I <sub>4</sub> interrupt input signal. This allows<br>positive control of data transfers from the microprocessor to the<br>peripheral device. |

| 0               | 1               | Pulse Output            | CB goes low for IMS after a microprocessor "Write B Data" operation.<br>This can be used to signal the peripheral device that data is available.                                                                                                         |

| 1               | 0               | Manual<br>Output        | CB set low.                                                                                                                                                                                                                                              |

| 1               | 1               | Manual<br>Output        | CB set high.                                                                                                                                                                                                                                             |

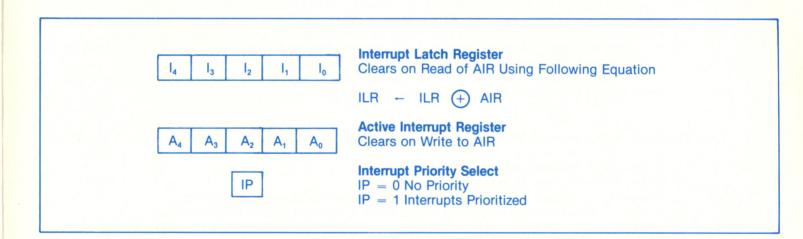

#### **INTERRUPT MASK REGISTER DESCRIPTION**

When the Interrupt Mode is selected (MC = 1), the Data Direction Register for Port C (DDRC) is used to enable or disable a corresponding interrupt input. For example: If  $M_0 = 0$  then  $I_0$  is disabled and any  $I_0$  interrupt latched in the interrupt latch register will not be transferred to the AIR and will not cause IRQ to go low. The interrupt latch can be cleared by writing a zero to the appropriate I bit in PRC.

# PORT REGISTER C DESCRIPTION

Port Register C (PRC) can operate in two modes. The mode is controlled by bit MC in register CR. When MC = 0, PRC is a standard I/O port, operating identically to PRA & PRB. If MC = 1, then port register C is used for hand-shaking and priority interrupt input and output.

# **PRC When MC** = 0:

| PC <sub>7</sub> | PC <sub>6</sub> | PC <sub>5</sub> | PC₄ | PC <sub>3</sub> | $PC_2$ | $PC_1$ | PC <sub>0</sub> |  |

|-----------------|-----------------|-----------------|-----|-----------------|--------|--------|-----------------|--|

|                 |                 |                 |     |                 |        |        |                 |  |

| PRC W | hen MC | = 1: |

|-------|--------|------|

|-------|--------|------|

| CB CA IRQ | I <sub>4</sub> | I <sub>3</sub> | <sub>2</sub> | $-I_1$ | l <sub>o</sub> |

|-----------|----------------|----------------|--------------|--------|----------------|

|-----------|----------------|----------------|--------------|--------|----------------|

#### **INTERRUPT EDGE CONTROL**

Bits  $IE_4$  and  $IE_3$  in the control register (CR) are used to determine the active edge which will be recognized by the interrupt latch.

If  $IE_4$  ( $IE_3$ ) = 0 then  $I_4$  ( $I_3$ ) latch will be set on a negative transition of  $I_4$  ( $I_3$ ) input.

If  $IE_4$  ( $IE_3$ ) = 1 then  $I_4$  ( $I_3$ ) latch will be set on a positive transition of the  $I_4$  ( $I_3$ ) input.

All other interrupt latches (I<sub>2</sub>, I<sub>1</sub>, I<sub>0</sub>) are set on a negative transition of the corresponding interrupt input.

## **FUNCTIONAL DESCRIPTION**

# 1. IP = 0 No Priority

All interrupt information latched into interrupt latch register (ILR) is immediately transferred into active interrupt register (AIR) and IRQ is pulled low. Upon read of interrupt register the IRQ is reset high and the appropriate bit(s) of the interrupt latch register is cleared by exclusive OR-ing. The ILR with AIR (ILR + AIR). After the appropriate interrupt request has been serviced a Write to the AIR will clear it and initiate a new interrupt sequence if any interrupts were received during previous interrupt servicing. In this non-prioritized mode it is possible for two or more interrupts to occur simultaneously and be transferred to the AIR. If this occurs it is a software effort to recognize this and act accordingly.

#### 2. IP = 1 Interrupts Prioritized

In this mode the Interrupt Inputs are prioritized in the following order  $I_4 > I_3 > I_2 > I_1 > I_0$

In this mode only one bit of the AIR can be set at any one time. If an interrupt occurs it is latched into the interrupt latch register, the IRQ line is pulled low and the appropriate bit of the AIR is set. To understand fully the operation of the priority interrupts it is easiest to consider the following examples.

- A. The first case is the simplest. A single interrupt occurs and the processor can service it completely before another interrupt request is received.

- 1. Interrupt  $1_1$  is received.

- 2. Bit I<sub>1</sub> is set high in Interrupt Latch Register.

- 3. IRQ is pulled low.

- 4. A<sub>1</sub> is set high.

- 5. Processor recognizes IRQ and reads AIR to determine which interrupt occurred.

- 6. Bit  $I_1$  is reset and IRQ is reset to high.

- 7. Processor Services Interrupt and signals completion of Service routine by writing to AIR.

- 8. A<sub>1</sub> is reset low and interrupt sequence is complete.

#### B. The second case occurs when an interrupt has been received and a higher priority interrupt occurs. (See Note)

- 1. Interrupt  $I_1$  is received.

- 2. Bit I<sub>1</sub> is set high on the Interrupt Latch Register.

- 3. IRQ is pulled low and  $A_1$  is set high.

- 4. Processor recognizes IRQ and reads AIR to determine which interrupt occurred.

- 5. Bit  $I_1$  is reset and  $\overline{IRQ}$  is reset high.

- 6. Processor begins servicing  $I_1$  interrupt and the  $I_2$  interrupt is received.

- 7.  $A_2$  is set,  $A_1$  is reset low and IRQ is pulled low.

- 8. Processor has not yet completed servicing I<sub>1</sub> interrupt so this routine will be automatically stacked in 6500 stack queue when new IRQ for I<sub>2</sub> of interrupt is received.

- 9. Processor reads AIR to determine I<sub>2</sub> interrupt occurrence and bit I<sub>2</sub> of interrupt latch is reset.

- 10. Processor services I<sub>2</sub> interrupt, clears A<sub>2</sub> by writing AIR and returns from interrupt. Returning from interrupt causes 650X processor to resume servicing I<sub>1</sub> interrupt.

- 11. Upon clearing A<sub>2</sub> bit in AIR, the A<sub>1</sub> bit will not be restored to a one. Internal circuitry will prevent a lower priority interrupt from interrupting the resumed I<sub>1</sub>.

- C. The third case occurs when an interrupt has been received and a lower priority interrupt occurs.

- 1. Interrupt I<sub>1</sub> is received and latched.

- 2.  $\overline{IRQ}$  is pulled low and A<sub>1</sub> is set high.

- 3. Processor recognizes IRQ and reads AIR to determine that I<sub>1</sub> interrupt occurred.

- 4. Processor logic servicing I<sub>1</sub> interrupt during which I<sub>0</sub> interrupt occurs and is latched.

- 5. Upon completion of I<sub>1</sub> interrupt routine the processor writes AIR to clear A<sub>1</sub> to signal 6525 that interrupt service is complete.

- 6. Latch I<sub>0</sub> interrupt is transferred to AIR and IRQ is pulled low to begin new interrupt sequence.

**NOTE:** It was indicated that the 6525 will maintain Priority Interrupt information from previously serviced interrupts.

This is achieved by the use of an Interrupt Stack. This stack is pushed whenever a read of AIR occurs and is pulled whenever a write to AIR occurs. It is therefore important not to perform any extraneous reads or writes to AIR since this will cause extra and unwanted stack operations to occur.

The only time a read of AIR should occur is to respond to an interrupt request.

The only time a write of AIR should occur is to signal the 6525 that the interrupt service is complete.