950 Rittenhouse Rd., Norristown, PA 19403 • Tel.: 215/666-7950 • TLX 846-100 MOSTECHGY VAFG

# 6500 MICROPROCESSORS

# THE 6500 MICROPROCESSOR FAMILY CONCEPT ----

The 6500 Series Microprocessors represent the first totally software compatible microprocessor family. This family of products includes a range of software compatible microprocessors which provide a selection of addressable memory range, interrupt input options and on-chip clock oscillators and drivers. All of the microprocessors in the 6500 group are software compatible within the group and are bus compatible with the M6800 product offering.

The family includes six microprocessors with on-board clock oscillators and drivers and four microprocessors driven by external clocks. The on-chip clock versions are aimed at high performance, low cost applications where single phase inputs, crystal or RC inputs provide the time base. The external clock versions are geared for the multi processor system applications where maximum timing control is mandatory. All versions of the microprocessors are available in 1 MHz, 2 MHz ("A" suffix on product numbers), and 3 MHz ("B" suffix on product numbers) maximum operating frequencies.

### **FEATURES OF THE 6500 FAMILY**

- Single +5 volt supply

- N channel, silicon gate, depletion load technology

- · Eight bit parallel processing

- 56 Instructions

- · Decimal and binary arithmetic

- Thirteen addressing modes

- True indexing capability

- Programmable stack pointer

- Variable length stack

- Interrupt capability

- Non-maskable interrupt

- Use with any type or speed memory

- 8 BIT Bi-directional Data Bus

- Addressable memory range of up to 65K bytes

- "Ready" input (for single cycle execution)

- · Direct memory access capability

- Bus compatible with M6800

- Choice of external or on-board clocks

- 1 MHz, 2 MHz, and 3 MHz operation

- On-the-chip clock options

- \* External single clock input

- \* RC time base input

- \* Crystal time base input

- Pipeline architecture

| MEMBERS OF TH<br>(CPU) FAMILY | IE 6500 MICROPROCESSOR        | ORDER NUMBER: MXS 65XX      |

|-------------------------------|-------------------------------|-----------------------------|

| Microprocessors               | with On-Chip Clock Oscillator |                             |

| Model                         | Addressable Memory            |                             |

| R6502                         | 65K Bytes                     |                             |

| R6503                         | 4K Bytes                      |                             |

| R6504                         | 8K Bytes                      |                             |

| R6505                         | 4K Bytes                      | FREQUENCY RANGE             |

| R6506                         | 4K Bytes                      | NO SUFFIX = 1 MHz           |

| R6507                         | 8K Bytes                      | A = 2 MHz                   |

|                               | with Edward Too Bloom         | B = 3  MHz                  |

|                               | with External Two Phase       |                             |

| Clock Inputs                  |                               | MODEL DESIGNATOR            |

| Model                         | Addressable Memory            | $XX = 02, 03, 04, \dots 15$ |

| R6512                         | 65K Bytes                     |                             |

| R6513                         | 4K Bytes                      | PACKAGE DESIGNATOR          |

| R6514                         | 8K Bytes                      | C = CERAMIC                 |

| R6515                         | 4K Bytes                      | P = PLASTIC                 |

#### **COMMENTS ON THE DATA SHEET**

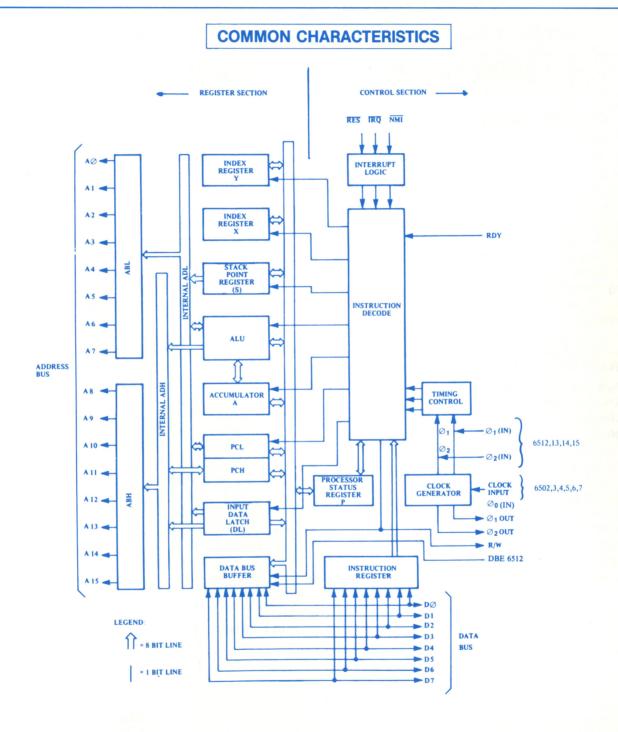

The data sheet is constructed to review first the basic "Common Characteristics"—those features which are common to the general family of microprocessors. Subsequent to a review of the family characteristics will be sections devoted to each member of the group with specific features of each.

Note: 1. Clock Generator is not included on 6512,13,14,15

2. Addressing Capability and control options vary with each of the 6500 Products.

# 6500 Internal Architecture

# **MAXIMUM RATINGS**

| RATING                | SYMBOL | VALUE        | UNIT |

|-----------------------|--------|--------------|------|

| SUPPLY VOLTAGE        | Vcc    | -0.3 to +7.0 | Vdc  |

| INPUT VOLTAGE         | Vin    | -0.3 to +7.0 | Vdc  |

| OPERATING TEMPERATURE | TA     | 0 to +70     | °C   |

| STORAGE TEMPERATURE   | TSTG   | -55 to +150  | °C   |

This device contains input protection against damage due to high static voltages or electric fields; however, precautions should be taken to avoid application of voltages higher than the maximum rating.

ELECTRICAL CHARACTERISTICS (Vcc = 5.0V  $\pm$  5%, Vss = 0, T<sub>A</sub> = 0° to + 70°C)  $\varnothing_1$ ,  $\varnothing_2$  (in) applies to 6512, 13, 14, 15;  $\varnothing_2$  (in) applies to 6502, 03, 04, 05, 06 and 07

| CHARACTERISTIC                                    | SYMBOL           | MIN.      | TYP. | MAX.       | UNIT                     |

|---------------------------------------------------|------------------|-----------|------|------------|--------------------------|

| Input High Voltage  Logic,⊘₀ (in)                 |                  | Vss + 2.4 | _    | Vcc        | Vdc                      |

| Ø₁,Ø₂(in)                                         | VIH              | Vcc - 0.2 | _    | Vcc + 1.0V | Vdc                      |

| Input High Voltage RES, NMI, RDY, IRQ, Data, S.O. |                  | Vss + 2.0 | _    | _          | Vdc                      |

| Input Low Voltage                                 |                  |           |      |            |                          |

| Logic,⊘。(in)                                      |                  | Vss - 0.3 | _    | Vss + 0.4  | Vdc                      |

| $\varnothing_1,\varnothing_2$ (in)                | VIL              | Vss - 0.3 | _    | Vss + 0.2  | Vdc                      |

| RES, NMI, RDY, IRQ, Data, S.O.                    |                  | _         | _    | Vss + 0.8  | Vdc                      |

| Input Leakage Current                             |                  |           |      |            |                          |

| (V <sub>In</sub> = 0 to 5.25V, Vcc = 5.25V)       |                  |           |      | 2.5        |                          |

| Logic (Excl. RDY,S.O.)<br>Ø₁,Ø₂(in)               | lin              |           |      | 100        | μ <b>Α</b><br>μ <b>Α</b> |

| ∅°(in)                                            |                  | _         | _    | 10.0       | μA                       |

|                                                   |                  |           |      |            | ·                        |

| Three State (Off State) Input Current             |                  |           |      |            |                          |

| $(V_{in} = 0.4 \text{ to } 2.4V, Vcc = 5.25V)$    | ITO              |           |      | 40         |                          |

| Data Lines                                        | ITSI             | _         | _    | 10         | μА                       |

| Output High Voltage                               |                  |           |      |            |                          |

| $(I_{OH} = -100\mu Adc, Vcc = 4.75V)$             |                  |           |      |            |                          |

| SYNC, Data, AO-A15, R/W                           | VOH              | Vss + 2.4 | _    | _          | Vdc                      |

| Out Low Voltage                                   |                  |           |      |            |                          |

| (I <sub>OL</sub> = 1.6mAdc, Vcc = 4.75V)          |                  |           |      |            |                          |

| SYNC, Data, AO-A15, RW                            | VOL              | _         | _    | Vss + 0.4  | Vdc                      |

| Power Dissipation                                 | P <sub>D</sub>   | _         | .35  | .80        | w                        |

| Capacitance                                       | С                |           |      |            | pF                       |

| $(V_{in} = O, T_A = 25^{\circ}C, f = 1MHz)$       |                  |           |      |            |                          |

| Logic                                             | C <sub>in</sub>  | _         | _    | 10         |                          |

| Data                                              |                  | _         | _    | 15         |                          |

| AO-A15,RW, SYNC                                   | C <sub>out</sub> | _         | _    | 12         |                          |

| Ø∘(In)                                            | C⊘∘(in)          | _         | _    | 15         |                          |

| ø. T                                              | c <sub>Ø</sub> , | _         | 30   | 50         |                          |

| Ø,                                                | C <sub>Ø</sub>   | _         | 50   | 80         |                          |

Note:  $\overline{\mbox{IRQ}}$  and  $\overline{\mbox{NMI}}$  require 3K pull-up resistors.

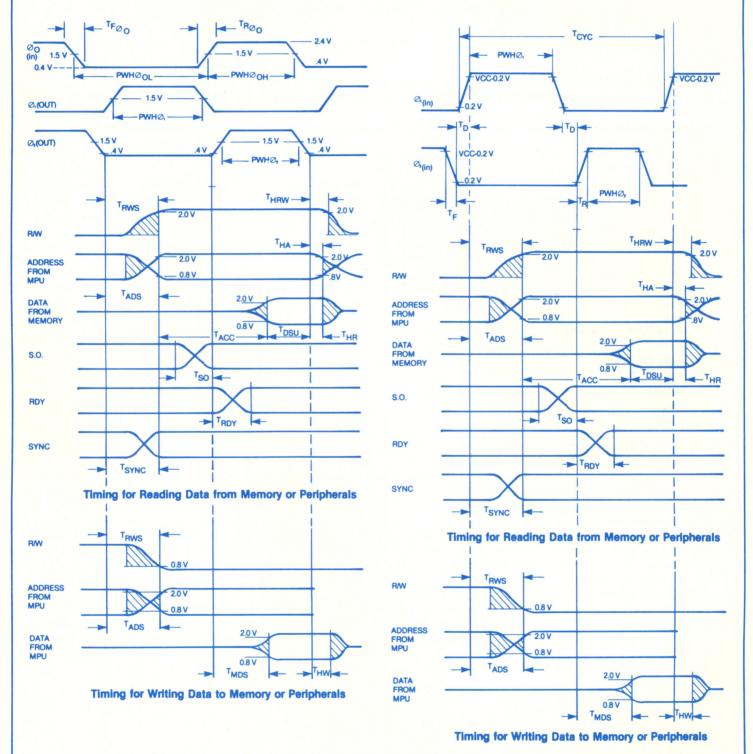

Clock Timing—MCS6512, 13, 14, 15

1 MH<sub>z</sub> TIMING

2 MH<sub>z</sub> TIMING

3 MH<sub>z</sub> TIMING

# Electrical Characteristics: (Vcc = 5V $\pm$ 5%, Vss = 0 V, $T_A$ = 0°-70°C)

#### CLOCK TIMING-6502, 03, 04, 05, 06, 07

| CHARACTERISTIC                                                                                               | SYMBOL                            | MIN.                    | TYP. | MAX.               |

|--------------------------------------------------------------------------------------------------------------|-----------------------------------|-------------------------|------|--------------------|

| Cycle Time                                                                                                   | ТСҮС                              | 1000                    | -    | -                  |

| Ø <sub>0(IN)</sub> Pulse Width (measured at 1.5v)                                                            | PWHØ <sub>0</sub>                 | 460                     | _    | 520                |

| Ø <sub>0 (IN)</sub> Rise, Fall Time                                                                          | TRØ <sub>0</sub> TFØ <sub>0</sub> | _                       | -    | 10                 |

| Delay Time between Clocks (measured at 1.                                                                    | 5v) T <sub>D</sub>                | 5                       | _    | -                  |

| Ø <sub>1(OUT)</sub> Pulse Width (measured at 1.5v)                                                           | PWHØ <sub>1</sub>                 | PWHØ <sub>OL</sub> - 20 | _    | PWHØ <sub>OL</sub> |

| Ø <sub>2(OUT)</sub> Pulse Width (measured at 1.5v)                                                           | PWHØ <sub>2</sub>                 | PWHØOH-40               | _    | PWHØOH - 10        |

| ∅ <sub>1(OUT)</sub> , ∅ <sub>2(OUT)</sub> Rise, Fall Time<br>(measured .8v to 2.0v)<br>(Load ½ 30pf ⅓ 1 TTL) | T <sub>R</sub> , T <sub>F</sub>   | -                       | -    | 25                 |

| MIN.                    | TYP.        | MAX.                    |

|-------------------------|-------------|-------------------------|

| 500                     | _           | _                       |

| 240                     | _           | 260                     |

| _                       | _           | 10                      |

| 5                       | _           | _                       |

| PWHØ <sub>OL</sub> − 20 | _           | PWHØ <sub>OL</sub>      |

| PWHØ <sub>OH</sub> - 40 | 19 <u>8</u> | PWHØ <sub>OH</sub> - 10 |

| -                       | _           | 25                      |

|                         |             |                         |

| MIN                     | TYP. | MAX.                    | UNITS |

|-------------------------|------|-------------------------|-------|

| 333                     | -    | _                       | ns    |

| 160                     | _    | 170                     | ns    |

| _                       | -    | 10                      | ns    |

| 5                       | _    | _                       | ns    |

| PWHØ <sub>OL</sub> −20  | -    | PWHØ <sub>OL</sub>      | ns    |

| PWHØ <sub>OH</sub> − 40 | _    | PWHØ <sub>OH</sub> − 10 | ns    |

| -                       | -    | 25                      | ns    |

|                         |      |                         |       |

|                         |      |                         |       |

#### CLOCK TIMING-8512, 13, 14, 15

| CHARACTERISTIC                                 | SYMBOL                         | MIN. | TYP. | MAX. |

|------------------------------------------------|--------------------------------|------|------|------|

| Cycle Time                                     | ТСҮС                           | 1000 | _    | _    |

| Clock Pulse Width Ø1                           | PWH Ø1                         | 430  |      |      |

| (Measured at V <sub>CC</sub> − 0.2v) Ø2        | PWH Ø2                         | 470  |      |      |

| Fail Time, Rise Time                           |                                |      |      |      |

| (Measured from 0.2v to V <sub>CC</sub> - 0.2v) | T <sub>F</sub> ,T <sub>R</sub> | _    | -    | 25   |

| Delay Time between Clocks                      |                                |      |      |      |

| (Measured at 0.2v)                             | T <sub>D</sub>                 | 0    | -    | _    |

| MIN. | TYP. | MAX. |

|------|------|------|

| 500  | _    | _    |

| 215  |      |      |

| 235  | -    |      |

|      |      |      |

|      | -    | 15   |

|      |      |      |

| 0    | _    | _    |

| MIN.       | TYP. | MAX. | UNITS |

|------------|------|------|-------|

| 333        | _    | _    | ns    |

| 150<br>160 | _    | -    | ns    |

|            | _    | 15   | ns    |

| 0          | _    | _    | ns    |

#### READWRITE TIMING (LOAD = ITTL)

| CHARACTERISTIC                  | SYMBOL            | MIN. | TYP. | MAX. |

|---------------------------------|-------------------|------|------|------|

| Read/Write Setup Time from 6500 | TRWS              | _    | 100  | 300  |

| Address Setup Time from 6500    | TADS              | _    | 100  | 300  |

| Memory Read Access Time         | TACC              | _    | _    | 575  |

| Data Stability Time Period      | TDSU              | 100  | -    | _    |

| Data Hold Time—Read             | THR               | 10   | _    | _    |

| Data Hold Time—Write            | T <sub>HW</sub>   | 30   | 60   | _    |

| Data Setup Time from 6500       | T <sub>MDS</sub>  | _    | 150  | 200  |

| S.O. Setup Time                 | T <sub>S.O.</sub> | 100  | _    | 1    |

| SYNC Setup Time from 6500       | TSYNC             | _    | -    | 350  |

| Address Hold Time               | T <sub>HA</sub>   | 30   | 60   | _    |

| R/W Hold Time                   | THRW              | 30   | 60   | _    |

| RDY Setup Time                  | TRDY              | 100  | _    | _    |

| MIN. | TYP. | MAX. |

|------|------|------|

| _    | 100  | 150  |

| _    | 100  | 150  |

| _    | -    | 300  |

| 50   | _    | _    |

| 10   | _    | _    |

| 30   | 60   | _    |

| _    | 75   | 100  |

| 50   | _    | _    |

| _    | _    | 175  |

| 30   | 60   | _    |

| 30   | 60   | -    |

| 50   | _    | _    |

| MIN. | TYP. | MAX. | UNITS |

|------|------|------|-------|

| _    | 80   | 110  | ns    |

| _    | 80   | 125  | ns    |

| _    | _    | 170  | ns    |

| 50   | -    | _    | ns    |

| 10   | -    | _    | ns    |

| 10   | _    | _    | ns    |

| _    | 70   | 100  | ns    |

| 50   | _    | _    | ns    |

| _    | _    | 120  | ns    |

| 10   | 30   | _    | ns    |

| 10   | 30   | _    | ns    |

| _    | _    | 15   | ns    |

#### **6500 SIGNAL DESCRIPTION**

Clocks  $(\emptyset_1, \emptyset_2)$

The 651X requires a two phase non-overlapping clock that runs at the Vcc voltage level.

The 650X clocks are supplied with an internal clock generator. The frequency of these clocks is externally controlled.

Address Bus (A<sub>0</sub>-A<sub>15</sub>)

These outputs are TTL compatible, capable of driving one standard TTL load and 130 pf.

Data Bus (D<sub>0</sub>-D<sub>7</sub>)

Eight pins are used for the data bus. This is a bi-directional bus, transferring data to and from the device and peripherals. The outputs are tri-state buffers capable of driving one standard TTL load and 130pf.

**Data Bus Enable (DBE)**

This TTL compatible input allows external control of the tri-state data output buffers and will enable the microprocessor bus driver when in the high state. In normal operation DBE would be driven by the phase two  $(\varnothing_2)$  clock, thus allowing data output from microprocessor only during  $\varnothing_2$ . During the read cycle, the data bus drivers are internally disabled, becoming essentially an open circuit. To disable data bus drivers externally, DBE should be held low.

Ready (RDY)

This input signal allows the user to single cycle the microprocessor on all cycles except write cycles. A negative transition to the low state during or coincident with phase one  $(\emptyset_1)$  and up to 100ns after phase two  $(\emptyset_2)$  will halt the microprocessor with the output address lines reflecting the current address being fetched. This condition will remain through a subsequent phase two  $(\emptyset_2)$  in which the Ready signal is low. This feature allows microprocessor interfacing with low speed PROMS as well as fast (max. 2 cycle) Direct Memory Access (DMA). If Ready is low during a write cycle, it is ignored until the following read operation.

Interrupt Request (IRQ)

This TTL level input requests that an interrupt sequence begin within the microprocessor. The microprocessor will complete the current instruction being executed before recognizing the request. At that time, the interrupt mask bit in the Status Code Register will be examined. If the interrupt mask flag is not set, the microprocessor will begin an interrupt sequence. The Program Counter and Processor Status Register are stored in the stack. The microprocessor will then set the interrupt mask flag high so that no further interrupts may occur. At the end of this cycle, the program counter low will be loaded from address FFFE, and program counter high from location FFFF, therefore transferring program control to the memory vector located at these addresses. The RDY signal must be in the high state for any interrupt to be recognized. A  $3K\Omega$  external resistor should be used for proper wire-OR operation.

Non-Maskable Interrupt (NMI)

A negative going edge on this input requests that a non-maskable interrupt sequence be generated within the microprocessor. NMI is an unconditional interrupt. Following completion of the current instruction, the sequence of operations defined for IRQ will be performed, regardless of the interrupt mask flag status. The vector address loaded into the program counter, low and high, are locations FFFA and FFFB respectively, thereby transferring program control to the memory vector located at these addresses. The instructions loaded at these locations cause the microprocessor to branch to a non-maskable interrupt routine in memory.

$\overline{\text{NMI}}$  also requires an external  $3K\Omega$  resister to Vcc for proper wire-OR operations.

Inputs  $\overline{\text{IRQ}}$  and  $\overline{\text{NMI}}$  are hardware interrupt lines that are sampled during  $\mathcal{O}_2$  (phase 2) and will begin the appropriate interrupt routine on the  $\mathcal{O}_1$  (phase 1) following the completion of the current instruction.

Set Overflow Flag (S.O.)

A NEGATIVE going edge on this input sets the overflow bit in the Status Code Register. This signal is sampled on the trailing edge of  $\emptyset_1$ .

#### SYNC

This output line is provided to identify those cycles in which the microprocessor is doing an OP CODE fetch. The SYNC line goes high during  $\emptyset_1$  of an OP CODE fetch and stays high for the remainder of that cycle. If the RDY line is pulled low during the  $\emptyset_1$  clock pulse in which SYNC went high, the processor will stop in its current state and will remain in the state until the RDY line goes high. In this manner, the SYNC signal can be used to control RDY to cause single instruction execution.

#### Reset

This input is used to reset or start the microprocessor from a power down condition. During the time that this line is held low, writing to or from the microprocessor is inhibited. When a positive edge is detected on the input, the microprocessor will immediately begin the reset sequence.

After a system initialization time of six clock cycles, the mask interrupt flag will be set and the microprocessor will load the program counter from the memory vector locations FFFC and FFFD. This is the start location for program control.

After Vcc reaches 4.75 volts in a power up routine, reset must be held low for at least two clock cycles. At this time the RW and (SYNC) signal will become valid.

When the reset signal goes high following these two clock cycles, the microprocessor will proceed with the normal reset procedure detailed above.

#### **ADDRESSING MODES**

**ACCUMULATOR ADDRESSING**—This form of addressing is represented with a one byte instruction, implying an operation on the accumulator.

**IMMEDIATE ADDRESSING**—In immediate addressing, the operand is contained in the second byte of the instruction, with no further memory addressing required.

ABSOLUTE ADDRESSING—In absolute addressing, the second byte of the instruction specifies the eight low order bits of the effective address while the third byte specifies the eight high order bits. Thus, the absolute addressing mode allows access to the entire 65K bytes of addressable memory.

ZERO PAGE ADDRESSING—The zero page instructions allow for shorter code and execution times by only fetching the second byte of the instruction and assuming a zero high address byte. Careful use of the zero page can result in significant increase in code efficiency.

INDEXED ZERO PAGE ADDRESSING—(X, Y indexing)—This form of addressing is used in conjunction with the index register and is referred to as "Zero Page, X" or "Zero Page, Y." The effective address is calculated by adding the second byte to the contents of the index register. Since this is a form of "Zero Page" addressing, the content of the second byte references a location in page zero. Additionally, due to the "Zero Page" addressing nature of this mode, no carry is added to the high order 8 bits of memory and crossing of page boundaries does not occur.

INDEXED ABSOLUTE ADDRESSING—(X, Y indexing)—This form of addressing is used in conjunction with X and Y index register and is referred to as "Absolute, X," and "Absolute, Y." The effective address is formed by adding the contents of X and Y to the address contained in the second and third bytes of the instruction. This mode allows the index register to contain the index or count value and the instruction to contain the base address. This type of indexing allows any location referencing and the index to modify multiple fields resulting in reduced coding and execution time.

**IMPLIED ADDRESSING**—In the implied addressing mode, the address containing the operand is implicitly stated in the operation code of the instruction.

**RELATIVE ADDRESSING**—Relative addressing is used only with branch instructions and establishes a destination for the conditional branch.

The second byte of the instruction becomes the operand which is an "Offset" added to the contents of the lower eight bits of the program counter when the counter is set at the next instruction. The range of the offset is -128 to + 127 bytes from the next instruction.

INDEXED INDIRECT ADDRESSING—In indexed indirect addressing (referred to as (Indirect, X)), the second byte of the instruction is added to the contents of the X index register, discarding the carry. The result of this addition points to a memory location on page zero whose contents is the low order eight bits of the effective address. The next memory location in page zero contains the high order eight bits of the effective address. Both memory locations specifying the high and low order bytes of the effective address must be in page zero.

INDIRECT INDEXED ADDRESSING—In indirect indexed addressing (referred to as (Indirect), Y), the second byte of the instruction points to a memory location in page zero. The contents of this memory location is added to the contents of the Y index register, the result being the low order eight bits of the effective address. The carry from this addition is added to the contents of the next page zero memory location, the result being the high order eight bits of the effective address.

ABSOLUTE INDIRECT—The second byte of the instruction contains the low order eight bits of a memory location. The high order eight bits of that memory location is contained in the third byte of the instruction. The contents of the fully specified memory location is the low order byte of the effective address. The next memory location contains the high order byte of the effective address which is loaded into the sixteen bits of the program counter.

#### INSTRUCTION SET—ALPHABETIC SEQUENCE

| ADC<br>AND<br>ASL<br>BCC                      | Add Memory to Accumulator with Carry "AND" Memory with Accumulator Shift left One Bit (Memory or Accumulator) Branch on Carry Clear                                                | LDA Load Accumulator with Memory LDX Load Index X with Memory LDY Load Index Y with Memory LSR Shift One Bit Right (Memory or Accumulator)                                                                                   |

|-----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BCS<br>BEQ                                    | Branch on Carry Set Branch on Result Zero                                                                                                                                          | NOP No Operation                                                                                                                                                                                                             |

| BIT                                           | Test Bits in Memory with Accumulator                                                                                                                                               | ORA "OR" Memory with Accumulator                                                                                                                                                                                             |

| BMI<br>BNE<br>BPL<br>BRK<br>BVC               | Branch on Result Minus Branch on Result not Zero Branch on Result Plus Force Break Branch on Overflow Clear                                                                        | PHA Push Accumulator on Stack PHP Push Processor Status on Stack PLA Pull Accumulator from Stack PLP Pull Processor Status from Stack                                                                                        |

| BVS<br>CLC<br>CLD<br>CLI                      | Branch on Overflow Set<br>Clear Carry Flag<br>Clear Decimal Mode<br>Clear Interrupt Disable Bit                                                                                    | ROL Rotate One Bit Left (Memory or Accumulator) ROR Rotate One Bit Right (Memory or Accumulator) RTI Return from Interrupt RTS Return from Subroutine                                                                        |

| CLV<br>CMP<br>CPX<br>CPY<br>DEC<br>DEX<br>DEY | Clear Overflow Flag Compare Memory and Accumulator Compare Memory and Index X Compare Memory and Index Y Decrement Memory by One Decrement Index X by One Decrement Index Y by One | SBC Subtract Memory from Accumulator with Borrow SEC Set Carry Flag SED Set Decimal Mode SEI Set Interrupt Disable Status STA Store Accumulator in Memory STX Store Index X in Memory STY Store Index Y in Memory            |

| EOR<br>INC<br>INX<br>INY<br>JMP<br>JSR        | "Exclusive-or" Memory with Accumulator Increment Memory by One Increment Index X by One Increment Index Y by One Jump to New Location Jump to New Location Saving Return Address   | TAX Transfer Accumulator to Index X TAY Transfer Accumulator to Index Y TSX Transfer Stack Pointer to Index X TXA Transfer Index X to Accumulator TXS Transfer Index X to Stack Register TYA Transfer Index Y to Accumulator |

#### **PROGRAMMING MODEL** NV BDIZC PROCESSOR STATUS REG. "P" A **ACCUMULATOR** INDEX REGISTER . x INDEX REGISTER CARRY 1 = TRUE 15 → ZERO 1 = RESULT ZERO **PROGRAM COUNTER "PC"** PCH PCL → IRQ DISABLE 1 = DISABLE 7 → DECIMAL MODE 1 = TRUE 1 STACK POINTER ..s.. S BRK COMMAND → OVERFLOW 1 = TRUE → NEGATIVE 1 = NEG.

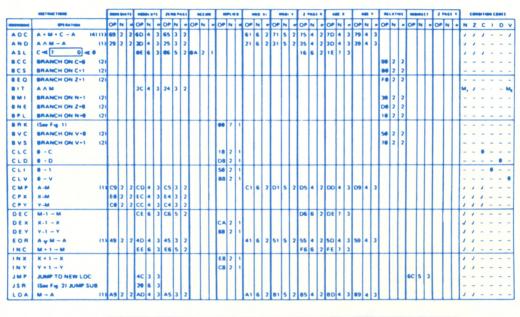

# INSTRUCTION SET - OP CODES, Execution Time, Memory Requirements

|       |                                                                          | -  | Q 004 | TE  | 400        |    | TE  | 240        | e N | 468 | •   | EE un | •                              |            | PAR | •  | -      | 10 1 | п   |        | 100 | Y 2,9661 1 686.1 |      |        | 400 | ٧      | 000          |    | MELATIVE |   | monne |    | Z,           | PAG | , ₹ |   | COMMITTE |     | <b>00</b> C |     | 18 |     |     |     |    |

|-------|--------------------------------------------------------------------------|----|-------|-----|------------|----|-----|------------|-----|-----|-----|-------|--------------------------------|------------|-----|----|--------|------|-----|--------|-----|------------------|------|--------|-----|--------|--------------|----|----------|---|-------|----|--------------|-----|-----|---|----------|-----|-------------|-----|----|-----|-----|-----|----|

| -     | SPE GATIGO                                                               | OP | N     | -   | OP         | N  |     | OP         | N   | •   | OP  | N     | •                              | OP         | N   | 4  | OP     | N    |     | OP     | N   | -                | OP I | N      | . 0 | PN     |              | O  | N        |   | O     | N  |              | OP  | N   |   | OP       | N   |             | N   | Z  | C   | 1   | C   | ,  |

| LDX   | M → X (1)                                                                | A2 | 2     | 2   | AE         | 4  | 3   | A6         | 3   | 2   |     |       | П                              |            |     | T  | ┪      | T    | ┪   |        | T   | T                |      | T      | Т   |        | Т            | 81 | E 4      | 3 | Г     | Т  | Т            |     | Г   |   | 86       | 4   | 2           | 7   | J  | -   | -   | -   |    |

| LDY   | M → Y (1)                                                                | AB | 2     | 2   | AC         | 4  | 3   | A4         | 3   | 2   |     | П     |                                |            | Н   | 1  |        | 1    | - 1 |        |     | П                | 84   | 4      | 2 8 | C 4    | 3            |    | 1        |   | ı     |    | ١            |     | l   |   |          | 1   | П           |     | 1  | -   | -   | -   |    |

| LSR   | • ► 7 0 ► C                                                              |    | П     | 1   | 4E         | 6  | 3   | 46         | 5   | 2   | 44  | 2     | ١                              |            | Н   | 1  | - 1    | 1    | -   |        | 1   | ı                | 56   | 6      | 2 5 | E 7    | 3            |    |          | ı | ı     | 1  | ı            | 1   | 1   |   |          | 1   | П           |     |    |     | -   |     |    |

| NOP   | NO OPERATION                                                             |    | Ш     | - 1 |            | П  | Н   |            | П   |     |     | П     |                                | EA         | 2   | 1  |        | -    | -1  |        |     | 1                |      | 1      | 1   |        | 1            | ı  | ı        | 1 | ı     |    | П            | ı   | ı   | П |          |     | П           | -   | -  | -   | -   |     |    |

| ORA   | AVM-A                                                                    | 09 | 2     | 2   | •D         | 4  | 3   | <b>0</b> 5 | 3   | 2   |     |       |                                |            |     | 1  | 01     | 6    | 2   | 11     | 5   | 2                | 15   | 4      | 2 1 | D 4    | 3            | 15 | 4        | 3 |       |    |              |     |     | П |          |     | П           | 1   | 4  | -   | -   |     |    |

| PHA   | A - Ms S-1 - S                                                           |    |       |     |            | П  | П   |            |     |     |     | П     | П                              | 48         | 3   | 1  | $\neg$ | 7    | 7   | $\neg$ | +   | †                |      | 1      | 1   | $\top$ | $^{\dagger}$ | t  | T        | T | ٢     |    | t            |     | T   | Г |          | T   | П           | -   | -  | -   | -   |     | -  |

| PHP   | P → Ms S-1 → S                                                           |    | П     | -   |            | П  | Н   |            | П   |     |     | Н     |                                | 88         | 3   | 1  |        |      |     |        |     | ١                |      |        |     |        | 1            | ı  | ı        |   | 1     |    |              | ı   |     | Н |          | 1   | П           | -   | _  | -   | -   |     |    |

| PLA   | S+1-S Ms-A                                                               |    | Ш     | ١   |            | П  | П   |            | П   | П   |     | Н     | 1                              | 68         | 4   | 1  |        |      | -   |        | 1   | 1                | - 1  |        | П   |        |              | ı  | ı        |   | ı     | 1  | ı            | ı   |     |   |          |     | П           |     |    | -   | -   |     |    |

| PLP   | S+1-S Ma-P                                                               |    | П     | 1   |            | П  | Н   |            | П   |     |     | Н     |                                | 28         | 4   | 1  |        |      | -   |        |     | ۱                | - 1  |        | 1   |        |              | ı  | ı        | 1 | ı     |    | ı            |     | 1   |   | ı        |     |             |     | IR | EST | TOF | REI | DI |

| ROL   | 7 0 - 0 -                                                                |    | Ш     | ۱   | 2E         | 6  | 3   | 26         | 5   | 2   | 2A  | 2     | 1                              |            |     | 1  |        |      |     |        | 1   | 1                | 36   | 6      | 2 3 | E 7    | 3            |    | 1        |   | 1     |    | ı            |     | 1   |   | ı        | 1   | П           | 1   |    |     | -   |     | -  |

| ROR   | -C-7 d-                                                                  |    | П     |     |            |    |     | 66         |     |     |     |       | 1                              |            | Н   | †  | _      | +    | 7   | $\neg$ | Ť   |                  |      |        |     | E 7    |              |    | Ť        | Ť | t     | +  | Ť            |     | T   | T |          | T   | Т           | 4   | 4  | d   | -   |     | _  |

| RTI   | (See Fig. 1) RTRN INT                                                    |    | П     | ١   |            |    | П   |            | П   |     |     |       |                                | 40         | 6   | 1  |        |      |     |        |     | 1                |      |        | 1   |        |              | ı  | ı        |   |       | 1  |              |     | 1   |   | 1        | 1   | П           |     | R  | EST | OF  | REC | 2) |

| RTS   | (See Fig. 2) RTRN SUB                                                    |    | Ш     |     |            | П  | Ш   |            | П   |     |     | Ш     |                                | 68         | 6   | 1  |        |      |     |        |     | 1                |      | -      | 1   |        | 1            | ı  | 1        |   | ı     |    |              | ı   |     |   | 1        |     |             | -   | -  | -   | -   |     | -  |

| SBC   | A-M-C - A (1)                                                            | E9 | 2     | 2   | ED         | 4  | 3   | E5         | 3   | 2   |     | Ш     |                                |            |     | 1  | E1     | 6    | 2   | F1     | 5   | 2                | F5   | 4      | 2 F | D      | 3            | F  | 9 4      | 3 |       |    | 1            | L   |     | ı | ı        | 1   | П           |     |    | 13  | ) - |     | -  |

| SEC   | 1 - C                                                                    |    | П     | ١   |            |    | Н   |            | П   |     |     | П     |                                | 38         | 2   | 1  |        | 1    | - 1 |        |     | ۱                |      | -      | 1   |        | П            | ı  |          | ı | ı     |    | ı            | 1   |     | ı | 1        | 1   | П           | -   | -  | 1   | -   |     | -  |

| SED   | 1 - D                                                                    |    |       |     |            |    | Н   |            |     |     |     |       |                                | F8         | 2   | 1  |        |      |     |        |     | 1                |      | -      | 1   |        |              | ı  |          |   | 1     |    |              | ı   | L   | ı |          |     |             | ۱-  | -  | -   | -   | - 1 | ı  |

| SEI   | 1-1                                                                      |    |       | Ī   |            |    | П   |            |     |     |     |       | П                              | 78         | 2   | 1  |        | 1    | ┪   |        | T   | 1                |      | $\top$ | 1   | 1      | T            | T  | T        |   |       |    | $^{\dagger}$ | T   | T   | T |          | T   | Т           | -   | -  | -   | 1   |     | -  |

| STA   | A - M                                                                    |    | П     |     | 80         | 4  | 3   | 85         | 3   | 2   |     | Ш     |                                |            | П   | ١  | 81     | 6    | 2   | 91     | 6   | 2                | 95   | 4      | 2 9 | D      | 3            | 9  | 9 5      | 3 | 3     |    |              |     | ı   | ı | 1        | 1   |             | ١-  | -  | -   | -   | -   | -  |

| STX   | X - M                                                                    |    | П     | 1   | 8E         | 4  | 3   | 86         | 3   | 2   |     | Н     |                                |            | Ш   | 1  |        |      | - 1 |        |     | ١                |      | -      | 1   |        | 1            |    |          |   | 1     |    | Т            |     |     | ı | 96       | 5 4 | 2           | 1 - | -  | -   | -   |     | -  |

| STY   | Y → M                                                                    |    | П     |     | <b>8</b> C | 4  | 3   | 84         | 3   | 2   |     |       |                                |            | П   |    |        | 1    | - 1 |        |     | ١                | 94   | 4      | 2   |        |              | 1  | 1        |   | 1     |    |              | 1   | L   |   |          |     |             | -   | -  | -   | -   |     | -  |

| TAX   | A - X                                                                    |    |       |     |            |    |     |            |     |     |     | Ш     |                                | AA         | 2   | 1  |        |      | - 1 |        | 1   | ۱                |      |        |     |        |              |    | 1        |   |       |    |              | L   | ı   | ı |          |     |             | 1   | J  | -   | -   |     | -  |

| TAY   | A - Y                                                                    |    |       |     |            |    |     |            |     |     |     |       |                                | <b>8</b> A | 2   | 1  | $\neg$ | T    | ╛   |        | T   | T                |      | Т      | Т   |        | Т            | T  | T        | T | Т     |    | T            | Т   | Т   | Т | Т        | T   | Т           | 1   | ,  | -   |     | -   | -  |

| TSX   | S - X                                                                    |    | П     | 1   |            | П  | П   |            | П   |     |     | П     |                                | BA         | 2   | ١  |        | 1    | - 1 |        | 1   | 1                |      |        |     |        |              | L  | 1        |   | 1     |    |              | П   | 1   |   |          |     |             | -   |    | -   |     | -   | -  |

| TXA   | X - A                                                                    |    | П     |     |            |    | l   |            | П   |     |     |       |                                | 88         | 2   | 1  |        | 1    | 1   |        |     | 1                |      |        |     |        |              | ı  |          | ı |       |    |              | ı   | ı   |   |          |     |             | 1   | ٠  | -   |     | -   | -  |

| TXS   | x - S                                                                    |    |       |     |            |    |     |            |     |     |     |       |                                | 9A         | 2   | 1  |        | ١    |     |        | 1   | 1                |      |        |     |        |              |    | 1        | 1 |       |    |              |     |     |   |          |     |             | -   | -  |     |     |     | -  |

| TYA   | Y - A                                                                    |    |       |     |            |    |     |            |     |     |     |       |                                | 98         | 2   | 1  |        |      | - 1 |        | -   | 1                |      |        |     |        |              |    |          |   |       |    | ı            | L   |     | П | 1        |     |             | -   |    |     |     | -   | -  |

| (2) A | DD 1 TO "N" IF PAGE BO<br>DD 1 TO "N" IF BRANCH<br>DD 2 TO "N" IF BRANCH | 00 | CU    | RS  | TC         | SA | AMI | E PA       |     |     | AGI | E     |                                |            | X I | NC | )E x   | ٧    |     | TOR    |     |                  |      |        |     |        |              |    |          |   | SU    | 81 | RA           | ст  |     |   |          |     | M           |     | OR | ١ و | ) T | 7   |    |

| (3) C | ARRY NOT - BELOW                                                         |    |       |     |            |    |     |            |     |     |     |       | M MEMORY PER EFFECTIVE ADDRESS |            |     |    |        |      |     |        |     |                  |      | V OR   |     |        |              |    |          |   | N     | N  | 0            | CY  | CLE | S |          |     |             |     |    |     |     |     |    |

|       | IN DECIMAL MODE 2 F                                                      |    |       |     |            |    |     | RO         | RE  | SU  | LT  |       |                                |            | Ms  | ME | MO     | AY   | PE  | A S    | TA  | CK               | PO   | IN     | TER |        |              |    |          | • |       | CL |              | VE  | OR  |   |          |     | N           | 0 1 | BY | res |     |     |    |

Note: MOS Technology cannot assume liability for the use of undefined OP Codes

| RES      | 1  | 28 | $\Rightarrow \phi_2 \text{ (OUT)}$ |

|----------|----|----|------------------------------------|

| VSS      | 2  | 27 | $\Box \phi_0$ (IN)                 |

| \$1.10UT | 3  | 26 | □ R/W                              |

| IRO      | 4  | 25 | <b>D</b> 00                        |

| VCC      | 5  | 24 | D1                                 |

| AO       | 6  | 23 | D2                                 |

| A1       |    | 22 | <b>□</b> D3                        |

| A2       | 8  | 21 | D4                                 |

| A3       | 9  | 20 | D5                                 |

| A4       | 10 | 19 | D6                                 |

| A5       | 11 | 18 | <b>D</b> 7                         |

| A6       | 12 | 17 | A11                                |

| A7       | 13 | 16 | → A10                              |

| A8       | 14 | 15 | □ A9                               |

|          |    |    |                                    |

# 6506-28 Pin Package

#### Features of 6506

- 4K Addressable Bytes of Memory (A0-A11)

- On-the-chip Clock

- IRQ Interrupt

- Two phase output clock for timing of support chips

- 8 Bit Bidirectional Data Bus

# 6507-28 Pin Package

#### Features of 6507

- 8K Addressable Bytes of Memory (A0-A12)

- On-the-chip Clock

- RDY Signal

- 8 Bit Bidirectional Data Bus

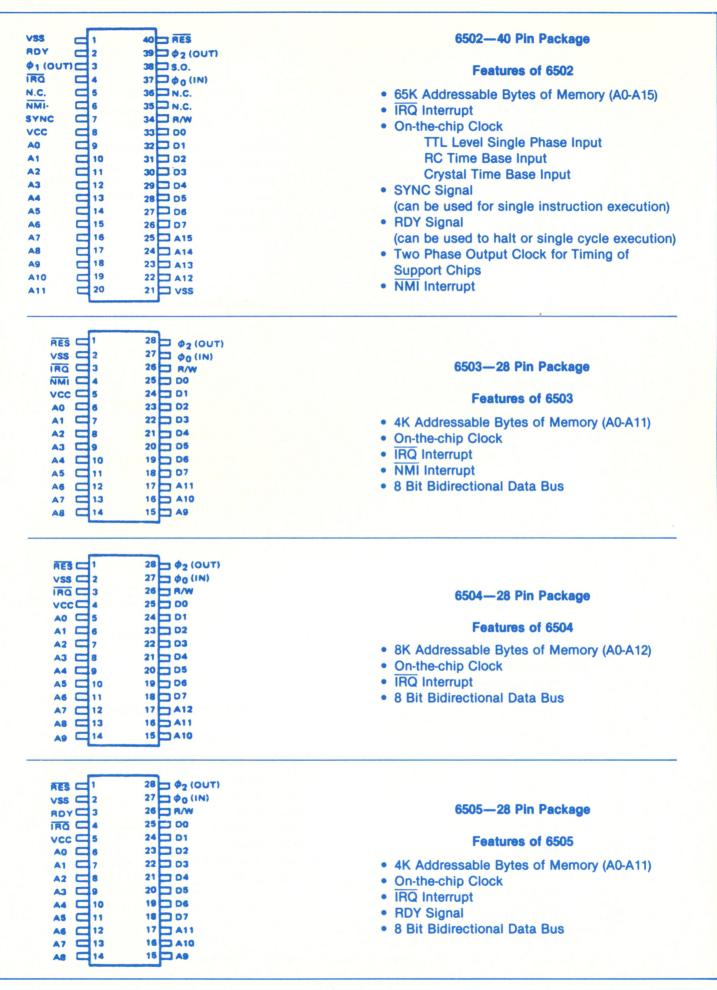

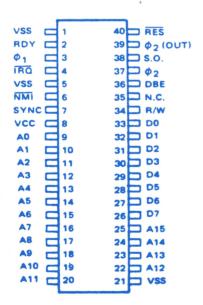

#### 6512-40 Pin Package

# Features of 6512

- 65K Addressable Bytes of Memory (A0-A15)

- IRQ Interrupt

- NMI Interrupt

- RDY Signal

- 8 Bit Bidirectional Data Bus

- SYNC Signal

- Two phase clock input

- Data Bus Enable

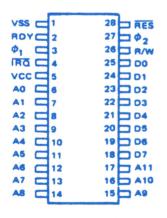

# 6513-28 Pin Package

#### Features of 6513

- 4K Addressable Bytes of Memory (A0-A11)

- Two phase clock input

- IRQ Interrupt

- NMI Interrupt

- 8 Bit Bidirectional Data Bus

#### 6514-28 Pin Package

#### Features of 6514

- 8K Addressable Bytes of Memory (A0-A12)

- Two phase clock input

- IRQ Interrupt

- 8 Bit Bidirectional Data Bus

# 6515—28 Pin Package

#### Features of 6515

- 4K Addressable Bytes of Memory (A0-A11)

- Two phase clock input

- IRQ Interrupt

- RDY Signal

- 8 Bit Bidirectional Data Bus

MOS TECHNOLOGY, INC. reserves the right to make changes to any products herein to improve reliability, function or design. MOS TECHNOLOGY, INC. does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights nor the rights of others.